Базовые цифровые устройства

Ланкевич Ю.Ю.

Базовые цифровые устройства

- Логические элементы (И, ИЛИ, НЕ, Исключающее ИЛИ)

- Комбинационные схемы:

- Дешифратор /Шифратор

- Мультиплексор/Демультиплексор

- Сумматор

- Компаратор

- Последовательностные схемы

- Триггеры

- Синхронные

- по фронту

- по уровню

- Асинхронные

- Синхронные

- Регистры

- Автоматы

- Счетчики

- Триггеры

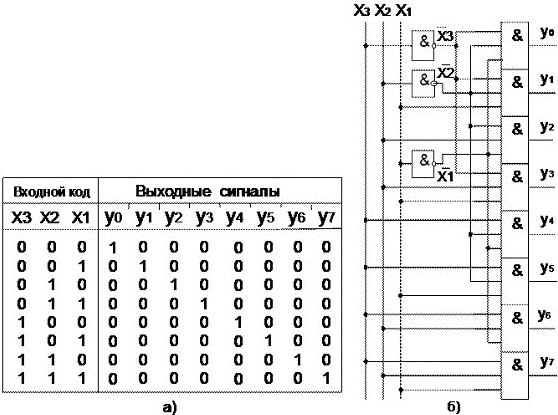

Дешифратор (VHDL модель)

- комбинационная схема, преобразующее n-разрядный двоичныйв -ичный одноединичный (позиционный) код

|

entity dc is port ( x : in std_logic_vector(2 downto 0); y : out std_logic_vector(7 downto 0)); end dc; architecture beh of dc is begin y <= "00000001" when x = "000" else "00000010" when x = "001" else "00000100" when x = "010" else "00001000" when x = "011" else "00010000" when x = "100" else "00100000" when x = "101" else "01000000" when x = "110" else "10000000" when x = "111" else "00000000"; end beh; |

|---|

library IEEE; use IEEE.STD_LOGIC_1164. all; use IEEE.NUMERIC_STD. all; entity Decoder is port ( Din : in STD_LOGIC_VECTOR (2 downto 0); Dout: out STD_LOGIC_VECTOR (7 downto 0)); end Decoder; architecture Synt of Decoder is begin Dout <= "00000001" sll TO_INTEGER (UNSIGNED(Din)); end Synt;

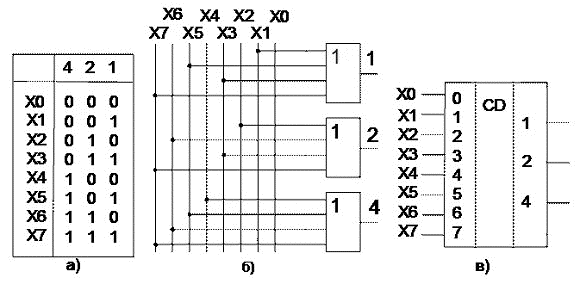

Шифратор

- комбинационная схема, выполняющее преобразование одноединичный (позиционного) n-разрядного кода в m-разрядный двоичный код.

|

|---|

Шифратор (VHDL модель 1)

| VHDL модель 1 | VHDL модель 2 |

|---|---|

entity cd is port ( x : in std_logic_vector(7 downto 0); y : out std_logic_vector(2 downto 0)); end dc; architecture beh1 of cd is begin y <= "000" when x(0) = "1" else "001" when x(1) = "1" else "010" when x(2) = "1" else "011" when x(3) = "1" else "100" when x(4) = "1" else "101" when x(5) = "1" else "110" when x(6) = "1" else "111" when x(7) = "1" else "000"; end beh1; |

entity cd is port ( x : in std_logic_vector(7 downto 0); y : out std_logic_vector(2 downto 0)); end dc; architecture beh2 of cd is begin y(0) <= x(1) or x(3) or x(5) or x(7); y(1) <= x(2) or x(3) or x(6) or x(7); y(2) <= x(4) or x(5) or x(6) or x(7); end beh2; |

Мультиплексор

- комбинационная схема, которая передает сигнал с одного из информационных входов Xi на единственный выход Y, причем номер выбираемого входа задается с помощью управляющих сигналов (адресных входов ai).

|

|---|

| y = OE(x0*a1*a0 + x1*a1*a0 + x2*a1*a0 + x3*a1*a0) |

Мультиплексор (Схема)

|

|---|

|

Мультиплексор (VHDL модель)

entity mux is port ( x : in std_logic_vector(3 downto 0); a : in std_logic_vector(1 downto 0); y : out std_logic); end mux; architecture beh of mux is begin y <= x(0) when a = "00" else x(1) when a = "01" else x(2) when a = "10" else x(3) when a = "11" else '0'; end beh;

library IEEE; use ieee.std_logic_1164.all; use ieee.numeric_std.all; entity Mux8 is port(x : in std_logic_vector(7 downto 0); a : in std_logic_vector(2 downto 0); y : out STD_LOGIC); end Mux8; architecture Synthesis_1 of Mux8 is begin process (x, a) begin y <= x(TO_INTEGER (UNSIGNED(a))); end process ; end Synthesis_1;

Мультиплексор (Особенность)

- с помощью мультиплексора можно реализовать любую логическую функцию

|

|---|

Демультиплексор

- комбинационная схема, которая выполняет функцию, обратную мультиплексору, т.е. в соответствии с принятой адресацией Ai направляет информацию с единственного входа D на один из M выходов Fj. При этом на остальных выходах будут логические нули (единицы).

| Входы | Выходы | ||||

|---|---|---|---|---|---|

| A1 | A0 | F3 | F2 | F1 | F0 |

| 0 | 0 | 0 | 0 | 0 | D |

| 0 | 1 | 0 | 0 | D | 0 |

| 1 | 0 | 0 | D | 0 | 0 |

| 1 | 1 | D | 0 | 0 | 0 |

Демультиплексор (Схема)

|

|

|

|---|

Демультиплексор (VHDL модель)

entity dms is port ( x : in std_logic; a : in std_logic_vector(1 downto 0); y : out std_logic_vector(3 downto 0)); end dms; architecture beh of dms is begin y <= "000" & x when a = "00" else "00" & x & '0' when a = "01" else '0' & x & "00" when a = "10" else x & "000" when a = "11" else "0000"; end beh;

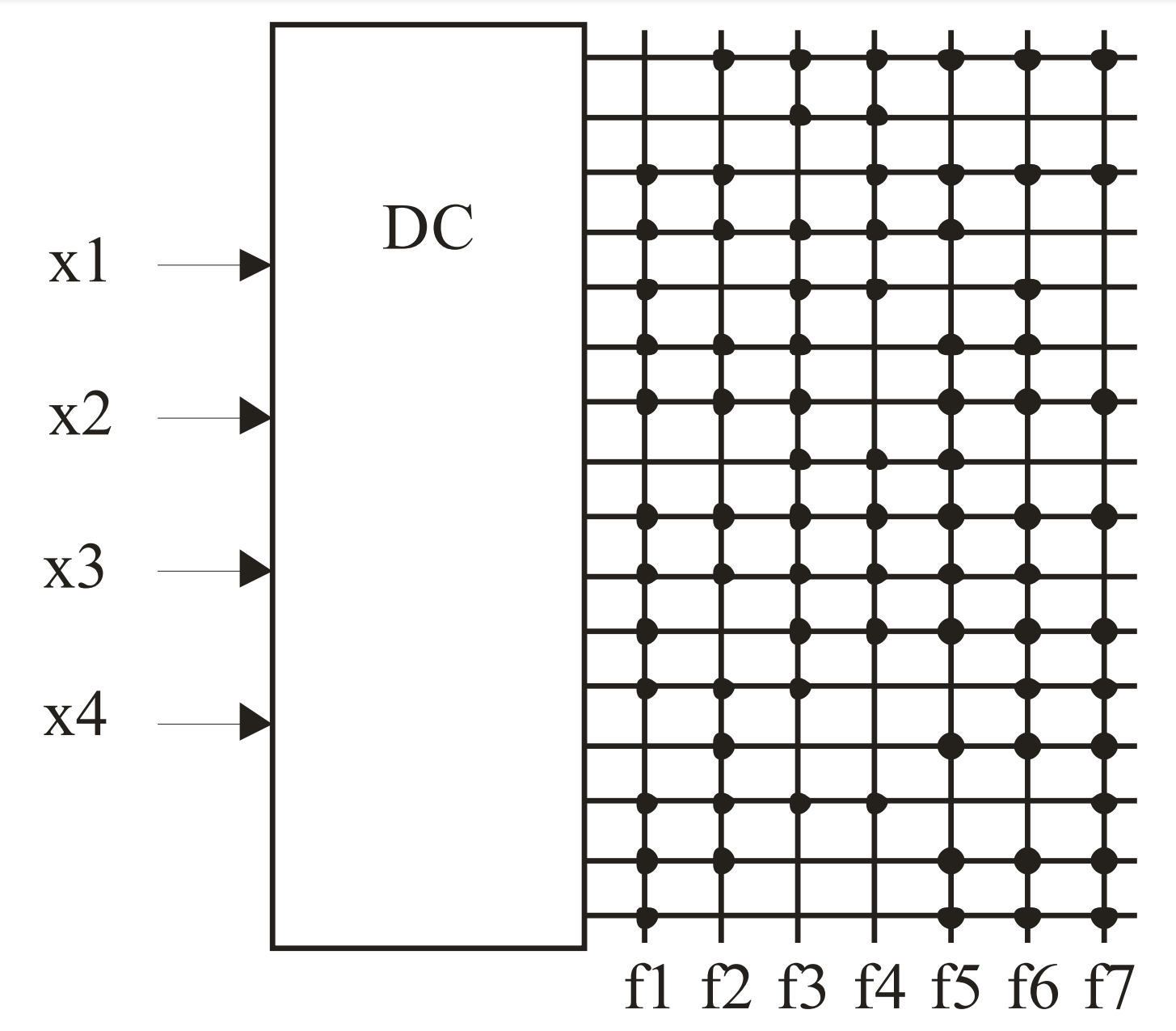

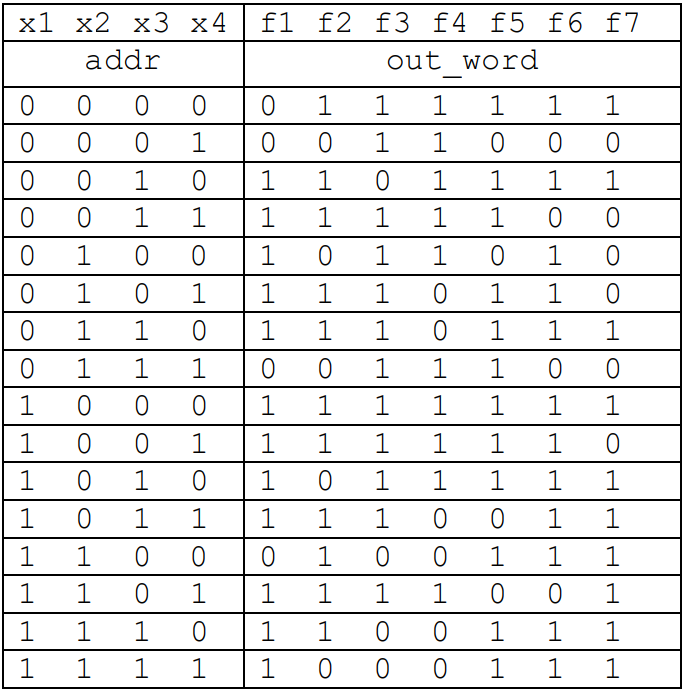

ПЗУ

ПЗУ(n,m) предназначено для хранения информации – 2n двоичных слов, каждое слово имеет m разрядов. Объем ПЗУ(n,m) – число бит хранимой информации подсчитывается по формуле

Заметим, что данная формула отражает сложность ПЗУ(n,m) весьма приближенно – в расчет не принимается сложность дешифратора.

На ПЗУ могут быть реализованы комбинационные схемы, функционирование которых представляется таблицей истинности системы булевых функций. При этом в ПЗУ "записывается" правая часть таблицы – значения функций на всех наборах булева пространства входных переменных.

Например, ПЗУ(4, 7), приведенное на рисунке, реализует функции, заданные данной таблицей истинности.

|

|

|---|

ПЗУ (VHDL модель)

Приведенное ниже описание (VHDL-код) позволяет моделировать конкретное ПЗУ(4, 7), т.е. ПЗУ, хранящее определенный набор двоичных словю.

Хранимые данные (биты) описываются константой hex_to_7 типа rom_type.

library work; use work.pack_rom.all; entity ROM7 is port (addr : in integer range 0 to 15; out_word : out seven_segment); end ROM7; architecture str of ROM7 is begin out_word <= hex_to_7 (addr) ; end str;

package pack_ROM is type seven_segment is array (6 downto 0) of bit ; type rom_type is array (natural range <>) of seven_segment ; constant hex_to_7 : rom_type (0 to 15) := ( "0111111", -- адрес 0 "0011000", -- адрес 1 "1101111", -- адрес 2 "1111100", -- адрес 3 "1011010", -- адрес 4 "1110110", -- адрес 5 "1110111", -- адрес 6 "0011100", -- адрес 7 "1111111", -- адрес 8 "1111110", -- адрес 9 "1011111", -- адрес 10 "1110011", -- адрес 11 "0100111", -- адрес 12 "1111001", -- адрес 13 "1100111", -- адрес 14 "1000111"); -- адрес 15 end pack_ROM; package body pack_ROM is end pack_ROM;

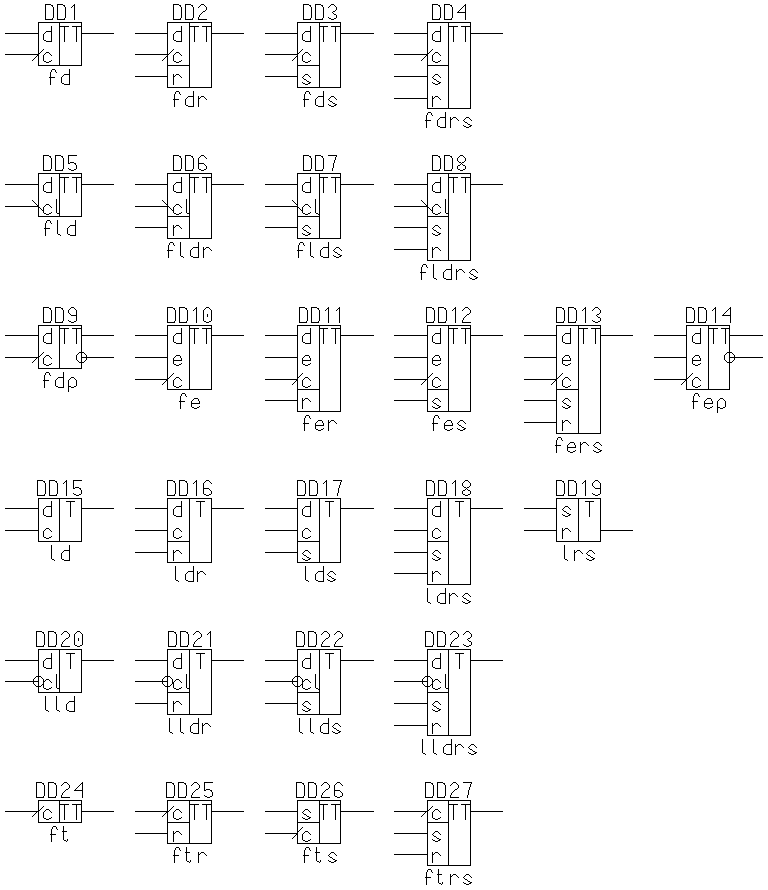

Классификация триггеров

VHDL-минимум для описания триггеров (1)

- Атрибуты — это различные характеристики объектов VHDL

| Атрибут | Описание |

|---|---|

| S'active | TRUE, если было присвоение, но текущее значение еще прежнее |

| S'delayed(t) | Значение сигнала, существовавшее на время t перед вычислением данного атрибута |

| S'event | TRUE, если происходит изменение сигнала |

| S'last_active | Время от последнего присвоения значения сигналу до момента вычисления атрибута |

| S'last_event | Время от последнего изменения сигнала до момента вычисления атрибута |

| S'last_value | Последнее присвоенное сигналу значение |

| S'stable(t) | TRUE, если не происходило изменение сигнала в течение времени t |

| S'transaction | TRUE, если происходит очередное присвоение значения сигналу |

| S'quiet | FALSE, если было присвоение, но текущее значение еще прежнее |

VHDL-минимум для описания триггеров (2)

- задание (выделение) фронта сигнала

clock_edge ::= RISING_EDGE(clk_signal_name) или FALLING_EDGE(clk_signal_name) или clock_level and event_expr или event_expr and clock_level

clock_level ::= clk_signal_name = '0' или clk_signal_name = '1' event_expr ::= clk_signal_name'EVENT или not clk_signal_name'STABLE

- функции RISING_EDGE и FALLING_EDGE описаны для типов:

- BIT, BOOLEAN и др. (пакет STANDARD в VHDL'2008)

- std_logic, std_ulogic (std_logic_1164)

VHDL-минимум для описания триггеров (3)

| Положительный фронт (переход 0 → 1) |

|---|

RISING_EDGE(clk_signal_name) clk_signal_name'EVENT and clk_signal_name = '1' clk_signal_name = '1' and clk_signal_name'EVENT not clk_signal_name'STABLE and clk_signal_name = '1' clk_signal_name = '1' and not clk_signal_name'STABLE |

| Отрицательный фронт (переход 1 → 0) |

|---|

FALLING_EDGE(clk_signal_name) clk_signal_name'EVENT and clk_signal_name = '0' clk_signal_name = '0' and clk_signal_name'EVENT not clk_signal_name'STABLE and clk_signal_name = '0' clk_signal_name = '0' and not clk_signal_name'STABLE |

- Все записи в столбцах эквивалентны

VHDL-минимум для описания триггеров. Оператор Process (3)

- Оператор процесса

LABEL: process [ ( имя сигнала {, имя сигнала } ) ]

объявление в процессе

begin

последовательный оператор[ы]

end process;

- Пример

| Пример c process | Сокращённая запись |

|---|---|

entity A2 is port ( A, B : in std_logic; C : out std_logic); end A2; architecture beh of A2 is begin process (A, B) begin C <= A and B; end process; end beh; |

entity A2 is port ( A, B : in std_logic; C : out std_logic); end A2; architecture beh of A2 is begin C <= A and B; end beh; |

VHDL-минимум для описания триггеров. Оператор if

- Оператор условия if (последовательный оператор)

if Условие_1 then Выражение1 elsif Условие_2 then Выражение2 else Выражение3 end if;

| Пример 1 | Пример 2 |

|---|---|

IF (s0='0' AND s1='0') THEN output <= in0; ELSIF (s0='1' AND s1='0') THEN output <= in1; ELSE output <= 'X'; END IF; |

IF (s0='0' AND s1='0') THEN output <= in0; ELSE output <= 'X'; END IF; |

| Пример 3 | Пример 4 |

IF (s0='0' AND s1='0') THEN output <= in0; ELSIF (s0='1' AND s1='0') THEN output <= 'X'; END IF; |

IF (s0='0' AND s1='0') THEN output <= in0; END IF; |

VHDL-минимум для описания триггеров (4)

| D-Триггер без сброса |

|---|

DFF: process(CLOCK) begin if CLOCK'EVENT and CLOCK = '1' then Q <= D; -- тактироваие передним фронтом end if; end process; |

| D-Триггер со сбросом и установкой |

|---|

AS_DFF: process (CLOCK, RESET, SET) begin if RESET = '1' then Q <= '0'; elsif SET = '1' then Q <= '1'; elsif CLOCK'EVENT and CLOCK = '1' then Q <= D; end if; end process; |

VHDL-модели триггеров (fdp)

- D-Триггер, синхронизируемый положительным фронтом, с парафазным выходом

library ieee; use ieee.std_logic_1164.all; entity fdp is -- pragma synthesis_off generic ( del : time := 900 ps); -- pragma synthesis_on port ( d : in std_logic; c : in std_logic; q : out std_logic; qn : out std_logic); end fdp; architecture beh of fdp is begin p1 : process (c) begin if c'event and c = '1' then q <= to_x01(d) after del; qn <= not to_x01(d) after del; end if; end process p1; end beh; |

VHDL-модели триггеров (fld)

- D-Триггер, синхронизируемый отрицательным фронтом

library ieee; use ieee.std_logic_1164.all; entity fld is -- pragma synthesis_off generic ( del : time := 900 ps); -- pragma synthesis_on port ( d : in std_logic; c : in std_logic; q : out std_logic); end fld; architecture beh of fld is begin p1 : process (c) begin if c'event and c = '0' then q <= to_x01(d) after del; end if; end process p1; end beh; |

VHDL-модели триггеров (fdrs)

- D-Триггер, синхронизируемый положительным фронтом, с асинхронным сбросом и установкой

library ieee; use ieee.std_logic_1164.all; entity fdrs is -- pragma synthesis_off generic ( del : time := 900 ps); -- pragma synthesis_on port ( d : in std_logic; c : in std_logic; r : in std_logic; s : in std_logic; q : out std_logic); end fdrs; architecture beh of fdrs is begin p1 : process (r, s, c) begin if r = '1' then q <= '0' after del; elsif s = '1' then q <= '1' after del; elsif c'event and c = '1' then q <= to_x01(d) after del; end if; end process p1; end beh; |

- D-Триггер, синхронизируемый положительным фронтом, с асинхронным сбросом

library ieee; use ieee.std_logic_1164.all; entity fdr is -- pragma synthesis_off generic ( del : time := 900 ps); -- pragma synthesis_on port ( d : in std_logic; c : in std_logic; r : in std_logic; q : out std_logic); end fdr; architecture beh of fdr is begin ff : process (r, c) begin if r = '1' then q <= '0' after del; elsif c'event and c = '1' then q <= to_x01(d) after del; end if; end process ff; end beh; |

- D-Триггер (fdrp) с прямым и инверсным выходом, синхронизируемый положительным фронтом, с асинхронным сбросом

| — | library ieee; use ieee.std_logic_1164.all; entity fdrp is -- pragma synthesis_off generic ( del : time := 900 ps); -- pragma synthesis_on port ( d : in std_logic; c : in std_logic; r : in std_logic; q : out std_logic; qn: out std_logic); end fdrp; architecture beh of fdrp is begin ff : process (r, c) begin if r = '1' then q <= '0' after del; qn <= '1' after del; elsif c'event and c = '1' then q <= to_x01(d) after del; qn <= not to_x01(d) after del; end if; end process ff; end beh; |

|---|

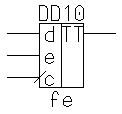

- D-Триггер с сигналом разрешения записи данных, синхронизируемый положительным фронтом

library ieee; use ieee.std_logic_1164.all; entity fe is -- pragma synthesis_off generic ( del : time := 900 ps); -- pragma synthesis_on port ( d : in std_logic; e : in std_logic; c : in std_logic; q : out std_logic); end fe; architecture beh of fe is begin p1 : process (c) begin if c'event and c = '1' then if e = '1' then q <= to_x01(d) after del; end if; end if; end process p1; end beh; |

- D-Триггер с сигналом разрешения записи данных, синхронизируемый положительным фронтом, с асинхронным сбросом и установкой

library ieee; use ieee.std_logic_1164.all; entity fers is -- pragma synthesis_off generic ( del : time := 900 ps); -- pragma synthesis_on port ( d : in std_logic; e : in std_logic; c : in std_logic; r : in std_logic; s : in std_logic; q : out std_logic); end fers; architecture beh of fers is begin p1 : process (r, s, c) begin if r = '1' then q <= '0' after del; elsif s = '1' then q <= '1' after del; elsif c'event and c = '1' then if e = '1' then q <= to_x01(d) after del; end if; end if; end process p1; end beh; |

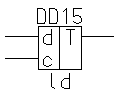

- D-Триггер, синхронизируемый положительным уровнем

library ieee; use ieee.std_logic_1164.all; entity ld is -- pragma synthesis_off generic ( del : time := 900 ps); -- pragma synthesis_on port ( d : in std_logic; c : in std_logic; q : out std_logic); end ld; architecture beh of ld is begin p1 : process (c, d) begin if c = '1' then q <= to_x01(d); end if; end process p1; end beh; |

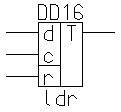

- D-Триггер, синхронизируемый положительным уровнем, с асинхронным сбросом

library ieee; use ieee.std_logic_1164.all; entity ldr is -- pragma synthesis_off generic ( del : time := 900 ps); -- pragma synthesis_on port ( d : in std_logic; c : in std_logic; r : in std_logic; q : out std_logic); end ldr; architecture beh of ldr is begin p1 : process (r, c, d) begin if r = '1' then q <= '0' after del; elsif c='1' then q <= to_x01(d) after del; end if; end process p1; end beh; |

- асинхронный RS-триггер

library ieee; use ieee.std_logic_1164.all; entity lrs is -- pragma synthesis_off generic ( del : time := 900 ps); -- pragma synthesis_on port ( r : in std_logic; s : in std_logic; q : out std_logic); end lrs; architecture beh of lrs is begin p1 : process (r, s) begin if r = '1' then q <= '0' after del; elsif s = '1' then q <= '1' after del; end if; end process p1; end beh; |

- D-Триггер, синхронизируемый низким уровнем

library ieee; use ieee.std_logic_1164.all; entity lld is -- pragma synthesis_off generic ( del : time := 900 ps); -- pragma synthesis_on port ( d : in std_logic; cl : in std_logic; q : out std_logic); end lld; architecture beh of lld is begin p1 : process (cl, d) begin if cl = '0' then q <= to_x01(d) after del; end if; end process p1; end beh; |

- T-триггер, синхронизируемый положительным фронтом

library ieee; use ieee.std_logic_1164.all; entity fts is -- pragma synthesis_off generic ( del : time := 900 ps); -- pragma synthesis_on port ( c : in std_logic; s : in std_logic; q : out std_logic); end fts; architecture beh of fts is signal q_i : std_logic; begin ff : process (s, c) begin if s = '1' then q_i <= '1' after del; elsif c'event and c = '1' then q_i <= not q_i after del; end if; end process ff; q <= q_i; end beh; |

Описание сдвигового регистра

entity reg is port ( di : in std_logic; d : in std_logic_vector(7 downto 0); shift_load : in std_logic; left_right : in std_logic; clk : in std_logic; -- reset reset : in std_logic; q : out std_logic_vector(7 downto 0); qi : out std_logic); end reg; architecture beh of reg is signal qq : std_logic_vector(7 downto 0); begin -- beh p1: process (clk, reset) begin -- process p1 if reset = '1' then qq(7 downto 0) <= "00000000"; -- (others => '0') elsif clk'event and clk = '1' then -- rising clock edge if shift_load = '0' then if left_right = '0' then qq <= qq(6 downto 0) & di ; qi <= qq(7); else -- left_right = '1' qq <= di & qq(7 downto 1); qi <= qq(0); end if; else -- shift_load = '1' - load mode qq <= d; end if; end if; end process p1; q <= qq; end beh;

Счетчики. Классификация

- Счетчиком называется цифровой блок, предназначенный для подсчета входных сигналов.

- Модуль счета: число возможных состояний счетчика.

Счетчики. Примеры VHDL описаний

entity IFSTMT is port ( RSTn, CLK, EN, PL : in bit; DATA : in integer range 0 to 31; COUNT : out integer range 0 to 31); end IFSTMT; architecture RTL of IFSTMT is signal COUNT_VALUE : integer range 0 to 31; begin p0 : process (RSTn, CLK) begin if (RSTn = '0') then COUNT_VALUE <= 0; elsif (CLK'event and CLK = '1') then if (PL = '1') then COUNT_VALUE <= DATA; elsif (EN = '1') then if (COUNT_VALUE = 31) then COUNT_VALUE <= 0; else COUNT_VALUE <= COUNT_VALUE + 1; end if; end if; end if; end process; COUNT <= COUNT_VALUE; end RTL;