LeonardoSpectrum...

Зайцев В.С.

Запуск GUI LS

- В Linux данная программа запускается под эмулятором wine.

- Поэтому для удобства создаём в файле .bshrc необходимый alias:

alias leonardo="wine /product_2008/mentor/win_xp/leonardo/bin/win32/leonardo.exe"

- Теперь можно запускать с консоли используя команду leonardo.

- В Win программа после установки запускается командой leonardo или командой spectrum в зависимости от версии софта.

- Иногда в эмуляторе wine отсутствует библиока MFC42.DLL, то при запуске wine выдает ошибки

- Для исправления необходимо в дирректорию /.wine/drive_c/windows/system32 скопировать из Windows недостающие файлы

Подключение библиотеки для синтеза

- Для синтеза должна быть создана специальная библиотека, как описано в Описание_библиотеки_синтеза_в_LeonardoSpectrum.

- Библиотека будет состоять из 2х файлов например:

devices.ini dr_lib.syn

- При этом файл devices.ini необходим для графического отображения в программе LS.

- Он содержит все описания билиотек, входящих в LS и туда необходимо дописать свою.

- Данные файлы необходимо скопировать в директорию <путь к программе LS>/lib.

- При этом файл devices.ini заменит уже имеющийся там такой же файл.

- Запускаем LS.

Лог подключения библиотеки

Последовательность действий при синтезе в GUI

![]() Имеется промоделированное vhdl-описание: counter.vhd. Из него необходимо получить синтезированный файл:

Имеется промоделированное vhdl-описание: counter.vhd. Из него необходимо получить синтезированный файл:

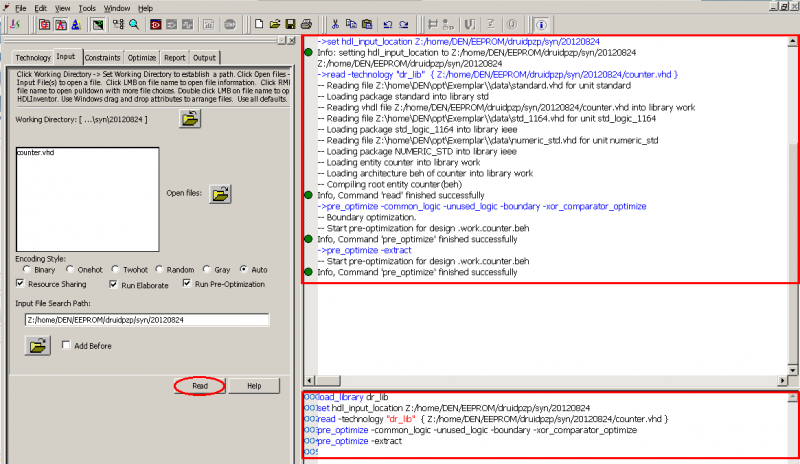

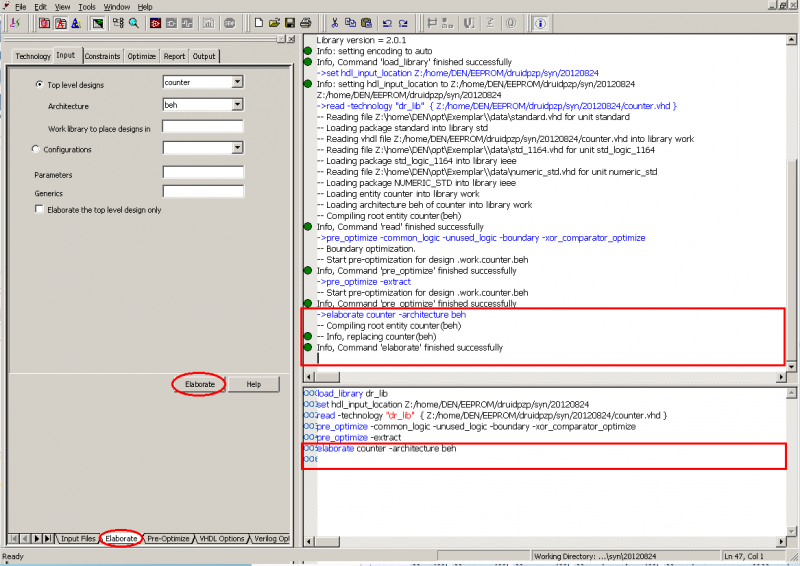

- Нажимаем вкладку Input

- Устанавливаем рабочую дерикторию Working Directory:[...\<путь к дерриктории>]

- Загружаем файл для синтеза ( counter.vhd)

- Устанавливаем тип кодирования автомата (state-machine)

- Устанавливаем путь к файлу (counter.vhd)

Файл поведенческого описания на vhdl

Файл для синтеза имеет следующий вид:

library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; entity counter is port ( clk1 : in std_logic; rst1 : in std_logic; dd_out : out std_logic_vector(7 downto 0); din_in : in std_logic_vector(7 downto 0); set1 : in std_logic); end counter; architecture beh of counter is signal dd : unsigned(7 downto 0); signal din : unsigned(7 downto 0); begin dd <= (others => '0') when rst1 = '1' else din when rst1 /= '1' and set1 = '1' else dd + 1 when clk1'event and clk1 = '1' else dd; dd_out <= std_logic_vector(dd); din <= unsigned(din_in); end beh;

Задаем временные ограничения

Задаем временные ограничения

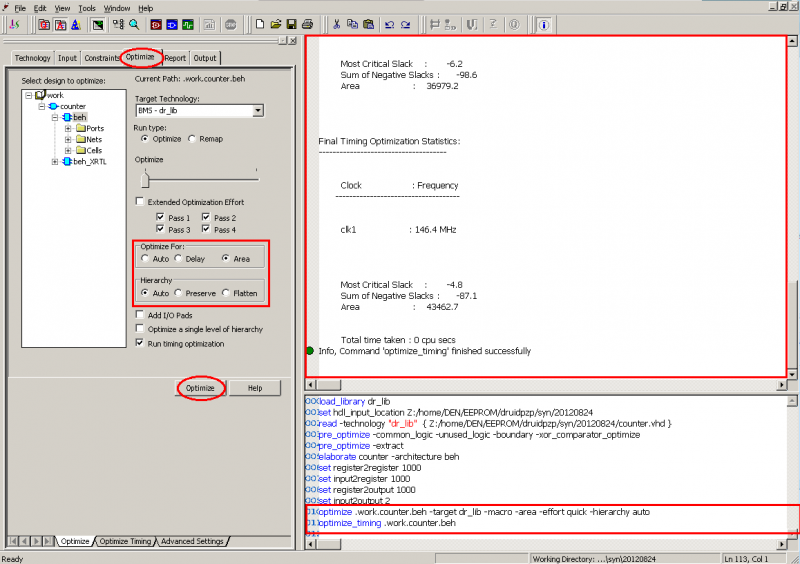

Оптимизация схемы

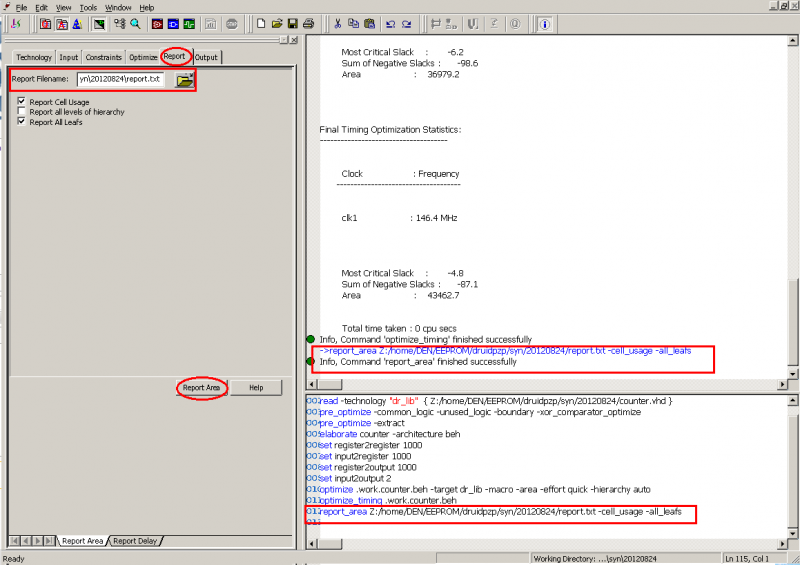

Сохранения логов и отчетов о синтезе

Пример файла отчета о результатах синтеза

Файл Report'а имеет следующий вид:

*******************************************************

Cell: counter View: beh Library: work

*******************************************************

Cell Library References Total Area

A2 dr_lib 1 x 440 440 um_2

DFFRS dr_lib 8 x 2696 21568 um_2

IX4 dr_lib 1 x 660 660 um_2

N dr_lib 19 x 220 4183 um_2

NA2 dr_lib 4 x 330 1321 um_2

NA3 dr_lib 2 x 440 881 um_2

NA4 dr_lib 2 x 550 1101 um_2

NAO2 dr_lib 8 x 440 3523 um_2

NO2 dr_lib 8 x 330 2642 um_2

NO3 dr_lib 5 x 440 2202 um_2

NO4 dr_lib 1 x 539 539 um_2

NOA2 dr_lib 4 x 440 1761 um_2

NOA2A2 dr_lib 2 x 550 1101 um_2

XNOR2 dr_lib 1 x 771 771 um_2

XOR2 dr_lib 1 x 771 771 um_2

Number of ports : 19

Number of nets : 78

Number of instances : 67

Number of references to this view : 0

Total accumulated area :

Number of um_2 : 43463

Number of accumulated instances : 67

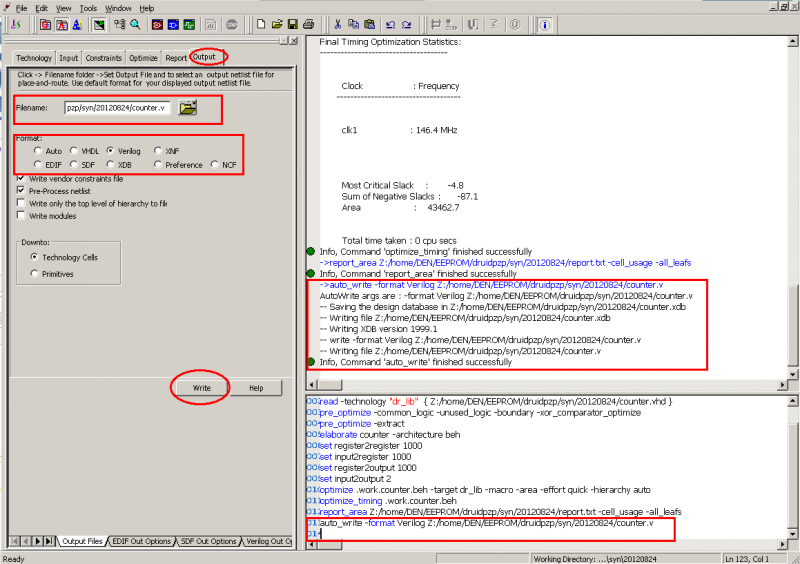

Сохранение результатов синтеза

Пример полученного после синтеза netlista

Фрагмент полученного файла в Формате Verilog имеет следующий вид:

// Verilog description for cell counter, // Fri 24 Aug 2012 02:05:57 PM EEST // // LeonardoSpectrum Level 3, 2003b.35 //module counter (clk1, rst1, dd_out, din_in, set1) ;

input clk1 ; input rst1 ; output [7:0]dd_out ; input [7:0]din_in ; input set1 ;^M wire NOT__178_, nx10, nx14, nx18, nx24, nx34, nx38, nx44, nx50, nx54, nx64, nx124, nx130, nx134, nx138, nx144, nx148, nx184, nx191, nx193, nx249, nx250, nx30, nx251, nx231, nx200, nx252, nx253, nx94, nx176, nx90, nx254, nx255, nx256, nx202, nx257, nx258, nx84, nx58, nx259, nx74, nx70, nx260, nx261, nx262, nx263, nx264, nx265, nx266, nx104, nx267, nx98, nx268, nx269, nx270, nx114, nx178, nx110, nx271; DFFRS reg_dd_0_ (.q (dd_out[0]), .c (clk1), .d (NOT__178_), .r (nx10), .s (nx14)) ; N ix174 (.y (NOT__178_), .d (dd_out[0])) ; NAO2 ix11 (.y (nx10), .d0 (din_in[0]), .d1 (nx271), .d2 (nx178)) ; NO2 ix15 (.y (nx14), .d0 (nx271), .d1 (nx10)) ; DFFRS reg_dd_1_ (.q (dd_out[1]), .c (clk1), .d (nx24), .r (nx30), .s (nx34) ; NOA2 ix25 (.y (nx24), .d0 (NOT__178_), .d1 (nx184), .d2 (nx18)) ; N ix185 (.y (nx184), .d (dd_out[1])) ; NO2 ix35 (.y (nx34), .d0 (nx271), .d1 (nx251)) ; DFFRS reg_dd_2_ (.q (dd_out[2]), .c (clk1), .d (nx44), .r (nx50), .s (nx54)) ; NOA2 ix45 (.y (nx44), .d0 (nx191), .d1 (nx193), .d2 (nx38)) ; NA2 ix192 (.y (nx191), .d0 (dd_out[1]), .d1 (dd_out[0])) ;

Просмотр полученной схемы

Синтез с помощью TCL-скрипта

Пример tcl скрипта

Полученный Файл имеет следующий вид:

load_library dr_lib set hdl_input_location Z:/home/DEN/EEPROM/druidpzp/syn/20120824 read -technology "dr_lib" { Z:/home/DEN/EEPROM/druidpzp/syn/20120824/counter.vhd } pre_optimize -common_logic -unused_logic -boundary -xor_comparator_optimize pre_optimize -extract elaborate counter -architecture beh set register2register 1000 set input2register 1000 set register2output 1000 set input2output 2 optimize .work.counter.beh -target dr_lib -macro -area -effort quick -hierarchy auto optimize_timing .work.counter.beh report_area Z:/home/DEN/EEPROM/druidpzp/syn/20120824/report.txt -cell_usage -all_leafs auto_write -format Verilog Z:/home/DEN/EEPROM/druidpzp/syn/20120824/counter.v view_schematic -view view_schematic -rtl -view

- В меню File->Run Script можно запустить данный скрипт и он сделает всё то, что было до этого настроено в GUI.

big>Report Area