Спец курс (Избранные главы VHDL)/Лабораторные работы — различия между версиями

Материал из Wiki

Vidokq (обсуждение | вклад) (→Задание 2-2) |

Vidokq (обсуждение | вклад) (→Задание 3) |

||

| Строка 92: | Строка 92: | ||

[[Файл:Eof_1-256.jpg|600px]] | [[Файл:Eof_1-256.jpg|600px]] | ||

| − | ==Задание 3== | + | ==Задание 3-1== |

| − | + | # Разработать синтезируемое VHDL-описание блока кодирования данных. | |

| + | ## Входные порты: D_I, clk, rst. | ||

| + | ## Выходные порты: D_O, возможно добавление доп. сигналов обратной связи. | ||

| + | # Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL). | ||

| + | ## Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I. | ||

| + | ## Блок формирования тактового сигнала. | ||

| + | ## Блок формирования сигнала сброса по питанию. | ||

| + | # Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script). | ||

| + | |||

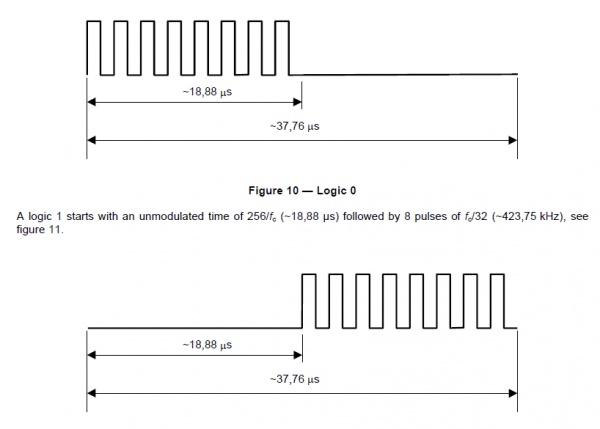

| + | * Тип выходной кодировки 1-256 (iso-15693-2) [[Файл:ISO15693-2.pdf]] | ||

| + | |||

| + | [[Файл:Manchester_cod.jpg|600px]] | ||

| + | |||

| + | * Частота тактового сигнала 13.56 MHz | ||

| + | * Перед стартом передачи данных посылать SOF | ||

| + | |||

| + | [[Файл:Sof_manchester_kod.jpg|600px]] | ||

| + | |||

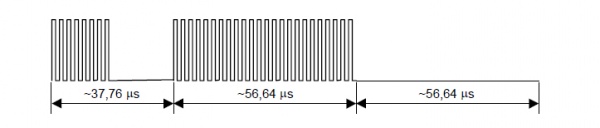

| + | * После завершения передачи данных EOF | ||

| + | |||

| + | [[Файл:Eof_manchester_kod.jpg|600px]] | ||

| + | |||

| + | ==Задание 3-2 == | ||

| + | # Разработать синтезируемое VHDL-описание блока декодирования данных. | ||

| + | ## Входные порты: D_I, clk, rst. | ||

| + | ## Выходные порты: D_O, возможно добавление доп. сигналов обратной связи. | ||

| + | # Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных. (Можно на SystemC, можно и на VHDL). | ||

| + | ## Тестовое окружение содержит в себе блок записи принимаемых данных в файл. | ||

| + | ## Блок формирования тактового сигнала. | ||

| + | ## Блок формирования сигнала сброса по питанию. | ||

| + | # Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script). | ||

| + | |||

| + | * Тип входной кодировки 1-256 (iso-15693-2) [[Файл:ISO15693-2.pdf]] | ||

| + | |||

| + | [[Файл:Manchester_cod.jpg|600px]] | ||

| + | |||

| + | * Частота тактового сигнала 13.56 MHz | ||

| + | * Прием данных начинать после получения SOF | ||

| + | |||

| + | [[Файл:Sof_manchester_kod.jpg|600px| Символ SOF]] | ||

| + | |||

| + | * Прекращать прием после прихода символа EOF | ||

| + | |||

| + | [[Файл:Eof_manchester_kod.jpg|600px| Символ EOF]] | ||

==Задание 4== | ==Задание 4== | ||

Версия 14:37, 17 октября 2012

Содержание |

Задание 1-1

- Разработать синтезируемое VHDL-описание блока кодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

- Тип выходной кодировки 1-256 (iso-15693-2) Файл:ISO15693-2.pdf

- Частота тактового сигнала 13.56 MHz

- Перед стартом передачи данных посылать SOF

- После завершения передачи данных EOF

Задание 1-2

- Разработать синтезируемое VHDL-описание блока декодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных. (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок записи принимаемых данных в файл.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

- Тип входной кодировки 1-256 (iso-15693-2) Файл:ISO15693-2.pdf

- Частота тактового сигнала 13.56 MHz

- Прием данных начинать после получения SOF

- Прекращать прием после прихода символа EOF

Задание 2-1

- Разработать синтезируемое VHDL-описание блока кодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

- Тип выходной кодировки 1-256 (iso-15693-2) Файл:ISO15693-2.pdf

- Частота тактового сигнала 13.56 MHz

- Перед стартом передачи данных посылать SOF

- После завершения передачи данных EOF

Задание 2-2

- Разработать синтезируемое VHDL-описание блока декодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных. (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок записи принимаемых данных в файл.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

- Тип выходной кодировки 1-256 (iso-15693-2) Файл:ISO15693-2.pdf

- Частота тактового сигнала 13.56 MHz

- Перед стартом передачи данных посылать SOF

- После завершения передачи данных EOF

Задание 3-1

- Разработать синтезируемое VHDL-описание блока кодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

- Тип выходной кодировки 1-256 (iso-15693-2) Файл:ISO15693-2.pdf

- Частота тактового сигнала 13.56 MHz

- Перед стартом передачи данных посылать SOF

- После завершения передачи данных EOF

Задание 3-2

- Разработать синтезируемое VHDL-описание блока декодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных. (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок записи принимаемых данных в файл.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

- Тип входной кодировки 1-256 (iso-15693-2) Файл:ISO15693-2.pdf

- Частота тактового сигнала 13.56 MHz

- Прием данных начинать после получения SOF

- Прекращать прием после прихода символа EOF