Спец курс (Избранные главы VHDL)/Верификация описания

Материал из Wiki

- Заголовок

- Верификация описания.

- Автор

- Зайцев В.С.

- Нижний колонтитул

- Спец курс (Избранные главы VHDL)/Верификация описания

- Дополнительный нижний колонтитул

- Зайцев В.С., 13:16, 2 декабря 2013

Содержание |

Слайд:Методы верификации проекта

- Имитационная верификация - верификация с использованием моделирования

- Формальная верификация -проверка модели с целью доказательства ее корректности и эквивалентности спецификации

(Пример: пакет FormulPro ф. MentorGraphics, пакеты фирмы Verplex, www.verplex.com)

Слайд:Верификация описания

Слайд:Верификация описания:step

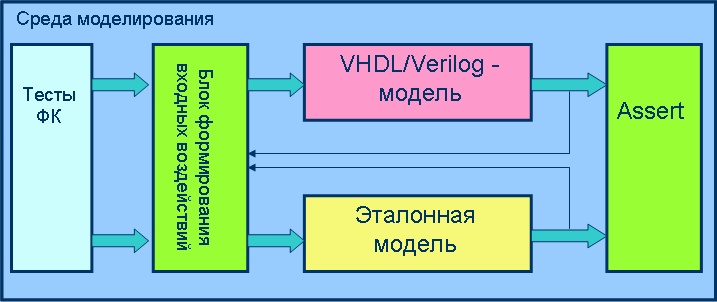

- Среда моделирования

- Active-HDL™

- Riviera-PRO™

- NC-Sim®

- ModelSim®

- QuestaSim®

- VCS-MX®

- Структура проекта

- Тестовое окружение

- RTL-модель (Verilog,VHDL)

- Эталонная модель (SystemC)

- Assert'ы (psl, OVVM, UVM)

- Отчеты и базы по результатам моделирования

Слайд: Типы тестов ФК

На что проверяем:

- Детерминистский - Проверяет обычные режимы работы системы, а также функционирование в граничных условиях на основе фиксированного набора тестов

- Случайный - Предполагает наличие генератора случайных входных воздействий

- Транзакционный - Фиксирует внимание на проверке интерфейсов и прохождению пакетов данных через них

Способ проведения проверки:

- "Черный ящик"

- "Серый ящик"

- "Прозрачный ящик"

Слайд:Средства верификации

- Прямые тесты (Directed tests)

- Псевдослучайные тесты (Random tests)

- Управляемые псевдослучайные тесты (Constrained Random tests)

- Верификация управляемая покрытием (на основе покрытия) (Coverage driven verification)

- Покрытие кода (Code coverage)

- Функциональное покрытие (Functional coverage )

- Верификация на основе утверждений (Assertion based verification)

- Эмуляция (Emulation)

- Формальная верификация (Formal verification)

Слайд: Полнота тестов

-

В реальных условия обычно полный перебор невозможен

В реальных условия обычно полный перебор невозможен

-

Поэтому поступают следующим образом. Например для сумматора:

Поэтому поступают следующим образом. Например для сумматора:

- Тестируют как "Серый ящик" и проверяют простейшие случаи 0+0, 0+1, FFFF+FFFF, 0+FFFF

- Затем целенаправленно проверяют граничные условия - переполнение, перенос

- Затем тестирую как "Черный ящик" на случайном наборе тестов

- Оценивают полноту проверки модели

Слайд: Метрики оценки полноты тестов

Необходимое условие : Управляемость (выполняется строка или переход) Достаточное условие : Наблюдаемость (результат исполнения влияет на выход сравниваемый с эталоном)

- Эвристические метрики - основанные на статистике появления ошибок

- календарное время между моментами обнаружения ошибок проекта (к концу процесса верификации оно увеличивается);

- общее количество промоделированных тактов работы проектируемого устройства;

- общее число обнаруженных ошибок в проекте и т.д.

- Программные метрики

- Полнота покрытия тестом строк кода модели

- Полнота покрытия переходов (число пополнений ветвей оператора if и case )

- Полнота покрытия путей (Branch coverage) (все пути в графе программы)

- Полнота покрытия выражений (Expression coverage) (оценка числа вычислений выражения по различных наборах)

- Полнота переключений из 0 в 1 и из 1 в 0 каждого бита (Toggle coverage)

- Автоматно-метрический подход (лучший вариант использовать формальную верификацию для автоматов)

- Моделирование неисправностей (в модель вносится неисправность)

- Мониторинг событий

Слайд: Метрики в ModelSim

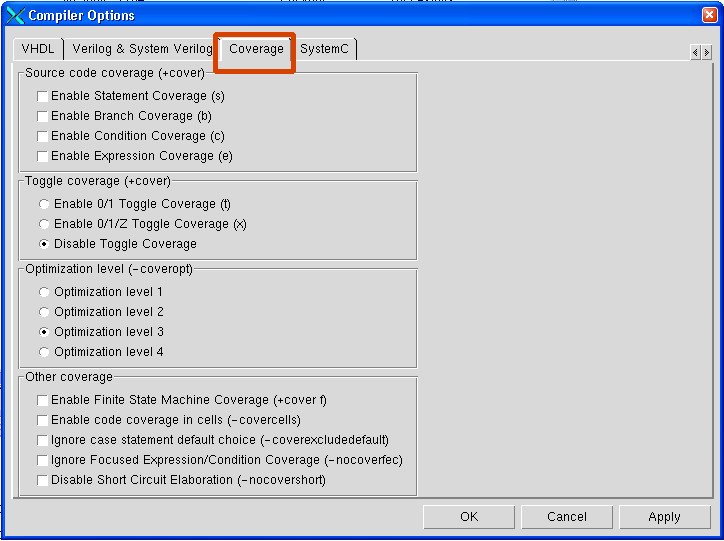

![]() В ModelSim для учета метрик покрытия при компиляции проекта нужно задать в меню Compile->Compiler option

В ModelSim для учета метрик покрытия при компиляции проекта нужно задать в меню Compile->Compiler option

Слайд: Виды покрытия кода в ModelSim

- Statement coverage — counts the execution of each statement on a line individually, even if there are multiple statements in a line.

- Branch coverage — counts the execution of each conditional “if/then/else” and “case” statement and indicates when a true or false condition has not executed.

- Condition coverage — analyzes the decision made in “if” and ternary statements and can be considered as an extension to branch coverage.

- Expression coverage — analyzes the expressions on the right hand side of assignment statements, and is similar to condition coverage.

- Toggle coverage — counts each time a logic node transitions from one state to another.

- FSM coverage — counts the states, transitions, and paths within a finite state machine.

Слайд:Эталонная модель на языке SystemC

- Высокий уровень абстракции

- Скорость моделирования

- Возможности языка C++

- Инструменты для автоматизации

- Совместное моделирование с другими HDL-языками