BIT-Cup 2015 (1 part) — версия для печати

Лист вопросов

Данный тест позволит вам проверить знания в VHDL

Вариант 2421608015.

Вопрос 1

Какое двоичное значение будет вырабатываться на выходе цифрового

устройства, описанного следующим VHDL-кодом:

library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_arith.all; entity dev is generic ( g : std_logic_vector := "101010000" ); port( q : out integer ); end dev; architecture behavioral of dev is begin q <= g'high; end behavioral;

- Описание является несинтезируемым

- 00000000000000000000000000001000

- 101010000

- 1

- 1000

Вопрос 2

Функционал какого цифрового блока описан следующим VHDL-кодом:

library ieee; use ieee.std_logic_1164.all; entity dev is port( a : in std_logic; b : in std_logic; c : in std_logic; q : out std_logic ); end dev; architecture behavioral of dev is signal s : std_logic; begin process(a,b,c) begin if rising_edge( a ) then if ( b = '1' ) then s <= c; end if; else s <= '0'; end if; end process; q <= s; end behavioral;

- Асинхронный D-триггер с синхронным сбросом

- Синхронный D-триггер с асинхронным сбросом

- Синхронный D-триггер с разрешением

- Описание является несинтезируемым

- Синхронный D-триггер с синхронным сбросом

Вопрос 3

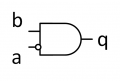

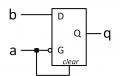

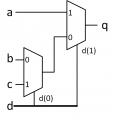

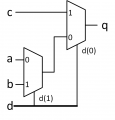

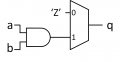

Какая схема будет является результатом синтеза следующего VHDL-описания:

library ieee; use ieee.std_logic_1164.all; entity dev is port( a : in std_logic; b : in std_logic; c : in std_logic; q : out std_logic ); end dev; architecture behavioral of dev is signal s : std_logic_vector( 4 downto 0 ); begin sch: for i in 4 downto 1 generate s( i-1 ) <= ( s( i ) and c ) when ( rising_edge( a ) ); end generate; s( 4 ) <= b; q <= s( 0 ); end behavioral;

- Схема 1

- Описание является несинтезируемым

- Схема 3

- Схема 2

- Схема 4

Вопрос 4

Функционал какого цифрового блока описан следующим VHDL-кодом:

library ieee; use ieee.std_logic_1164.all; entity dev is port( a : in std_logic; b : in std_logic; q : out std_logic ); end dev; architecture behavioral of dev is begin process( a,b ) begin if a='1' then if b='1' then q <= '1'; else q <= '0'; end if; else q <= '0'; end if; end process; end behavioral;

- Асинхронный D-триггер с разрешением

- 2-входовой элемент OR

- 2-входовой элемент NXOR

- Цифровой буфер с разрешением

- 2-входовой элемент AND

Вопрос 5

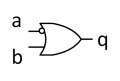

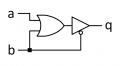

Какая схема будет является результатом синтеза следующего VHDL-описания:

library ieee; use ieee.std_logic_1164.all; entity dev is port( a : in std_logic; b : in std_logic; q : out std_logic ); end dev; architecture behavioral of dev is signal s : std_logic; begin process( a,b ) begin if ( a='1' ) then s <= '0'; end if; if ( a='0' ) then s <= b; end if; end process; q <= s; end behavioral;

- Схема 4

- Описание является несинтезируемым

- Схема 3

- Схема 2

- Схема 1

Вопрос 6

Функционал какого цифрового блока описан следующим VHDL-кодом:

library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity dev is port( a : in std_logic; b : in std_logic; q : out std_logic ); end dev; architecture behavioral of dev is constant s : std_logic_vector( 3 downto 0 ) := "1001"; signal c : std_logic_vector( 1 downto 0 ); begin c <= a & b; q <= s( conv_integer( c ) ); end behavioral;

- 4-разрядный регистр хранения

- 2-входовой элемент NXOR

- 2-входовой элемент NOR

- 4-битное асинхронное ПЗУ

- 4-разрядный регистр сдвига

Вопрос 7

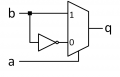

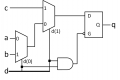

Какая схема будет является результатом синтеза следующего VHDL-описания:

library ieee; use ieee.std_logic_1164.all; entity dev is port( a : in std_logic; b : in std_logic; c : in std_logic; d : in std_logic_vector( 1 downto 0 ); q : out std_logic ); end dev; architecture behavioral of dev is begin process(a,b,c,d) begin if d="00" then q <= a; elsif d="01" then q <= b; elsif d="10" then q <= c; end if; end process; end behavioral;

- Схема 3

- Схема 4

- Схема 1

- Описание является несинтезируемым

- Схема 2

Вопрос 8

Функционал какого цифрового блока описан следующим VHDL-кодом:

entity dev is port( a : in std_logic_vector( 3 downto 0 ); q : out std_logic_vector( 1 downto 0 ); g : out std_logic ); end dev; architecture behavioral of dev is begin process( a ) variable v: std_logic_vector( 1 downto 0 ); begin v := "00"; for i in 3 downto 0 loop if ( a(i)='1' ) then v := conv_std_logic_vector( i, 2 ); g <= '1'; exit; else g <= '0'; end if; end loop; q <= v; end process; end behavioral;

- Мультиплексор 2х4

- Дешифратор 2х4

- Описание является несинтезируемым

- Сдвиговый асинхронный 4-разрядный регистр

- Приоритетный шифратор 4х2

Вопрос 9

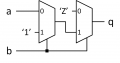

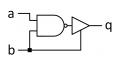

Какая схема будет является результатом синтеза следующего VHDL-описания:

library ieee; use ieee.std_logic_1164.all; entity dev is port( a : in std_logic; b : in std_logic; q : out std_logic ); end dev; architecture behavioral of dev is signal s : std_logic; begin s <= a when b='0' else '1'; q <= s when b='1' else 'Z'; end behavioral;

- Схема 2

- Схема 4

- Описание является несинтезируемым

- Схема 3

- Схема 1

Вопрос 10

Функционал какого цифрового блока описан следующим VHDL-кодом:

library ieee; use ieee.std_logic_1164.all; entity dev is port( a,b,c,d : in std_logic; q : out std_logic ); end dev; architecture behavioral of dev is signal s : std_logic; begin process( a,b,c,d,s ) begin if ( d = '1' ) then s <= '0'; elsif falling_edge( a ) then if ( b = '1' ) then if ( c = '1' ) then s <= not s; else s <= '1'; end if; elsif ( c = '1' ) then s <= '0'; end if; end if; end process; q <= s; end behavioral;

- D-триггер, управляемый спадом сигнала синхронизации с синхронным сбросом

- T-триггер, управляемый спадом сигнала синхронизации с асинхронным сбросом

- RS-триггер, управляемый фронтом сигнала синхронизации, с асинхронным сбросом

- JK-триггер, управляемый спадом сигнала синхронизации с асинхронным сбросом

- Описание является несинтезируемым

Форма для тестирования

Данный тест позволит вам проверить знания в VHDL

Вариант 2421608015.

| № | Ответ | Примечание |

|---|---|---|

| 1 | ||

| 2 | ||

| 3 | ||

| 4 | ||

| 5 | ||

| 6 | ||

| 7 | ||

| 8 | ||

| 9 | ||

| 10 |