Спец курс (Избранные главы VHDL)/Вспомним VHDL

Материал из Wiki

- Заголовок

- Вспомнить все...

- Автор

- Зайцев В.С.

- Нижний колонтитул

- Спец курс (Избранные главы VHDL)/Вспомним VHDL

- Дополнительный нижний колонтитул

- Зайцев В.С., 00:27, 29 сентября 2015

Содержание |

Total Recall

Слайд:Языки описания аппаратуры

- С начала 70-х годов стала актуальна проблема создания стандартного средства документации схем и алгоритмов дискретных систем переработки информации, пригодных как для восприятия человеком, так и для обработки в ЭВМ.

- Этим средством явились языки VHDL и Verilog

- Стандартность (лучше плохой, чем никакого)

- Многоаспектность и многоуровневость

- Схемы

- Тестовые окружения

- Диапазон детализации

- Человеко-машинность

- Язык описания

- Средство документирования

- Было много предшественников

- «МОДИС », «Автокод», «Модис-В78», «MPL», «OCC-2», «Форос», «Алгоритмы», «Пульс», «Симпатия»

- CDL, DDL, ISPS, CONLAN, HILO

VHDL ссылки и литература

Все примеры взяты с сайта БГУИР

Сайт БГУИР с материалами по VHDL

Слайд: Entity

library ieee; use ieee.std_logic_1164.all; entity xc is port ( clk : in std_logic; d : out std_logic); end xc;

Слайд: Architecture

architecture beh of trig is begin -- beh end beh;

Слайд: Process

trig_process: process (clk, rst) begin -- process trig_process if rst = '0' then -- asynchronous reset (active low) data_out <= '0'; elsif clk'event and clk = '1' then -- rising clock edge data_out <= data_in; end if; end process trig_process; |

Слайд: When Else

t1 <= not t1 when clk'event and clk = '1' else t1;

Данная запись является компактным описанием счетного триггера, но она не соответствует стандарту синтезируемого подмножества. Поэтому не все системы синтеза её поддерживают. Например, Leonardo Spectrum синтезирует данную конструкцию, а в ранних версиях Synopsys`а эта запись не поддерживалась.

Примеры кода на VHDL

Логическое ИЛИ

Слайд:Работа с редактором EMACS

Emacs (Ема́кс, Е́макс, также И́макс) — семейство многофункциональных расширяемых текстовых редакторов.

Слово «Emacs» берет начало в аббревиатуре «Editor MACroS», наборе макросов для редактора TECO, написанном Столлманом и другими в 1976 году

Слайд: Первый запуск

Команда для запуска

emacs

Слайд: Горячие клавиши

Слайд: Возможности :step

- Знает и подскажет базовые конструкции

- Подсветка синтаксиса

- Анализ существующего кода и добавление уже написанных "слов"

- Автоматическая генерация кода простейшего тестового окружения

- Добавление декларации component

- Добавление декларации instance

- Добавление декларации signal

- Возможность работы с консолью

- Возможность работы с с несколькими окнами одновременно

- И многое, многое другое полезное.

Слайд: Работа с системой моделирования QuestaSim от Mentor Graphics :step

- Где моделировать?

- QuestaSIM

- Язык VHDL, Verilog, SystemC, SystemVerilog

- Смешанное моделирование (все что выше + Spice)

- Автоматизация (поддерживаются скрипты TCL)

- Работа по сети (JobSpy сервер)

- Мощнейший инструмент верификации

- Покрытие кода

- Покрытие переходов

- Проверка значений

- Поддержка пакетов и стандарта верификации OVM

- Пакет моделирования подключается и в MentorGraphics и в Cadence

Слайд: Запуск QuestaSim

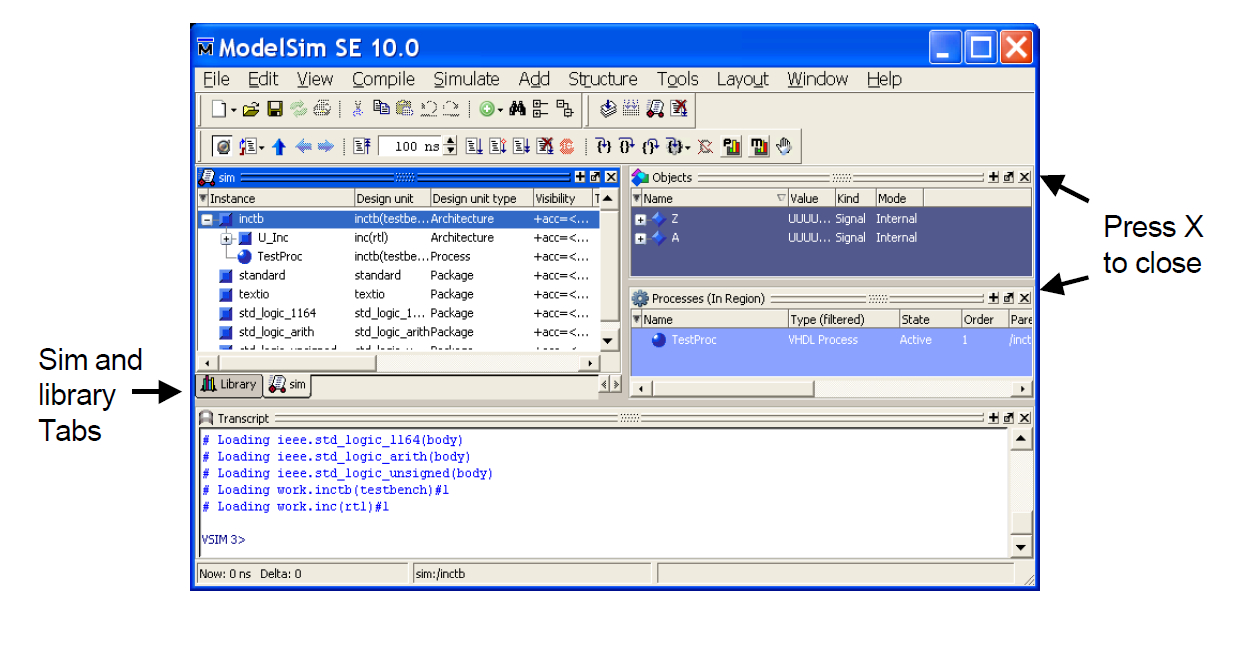

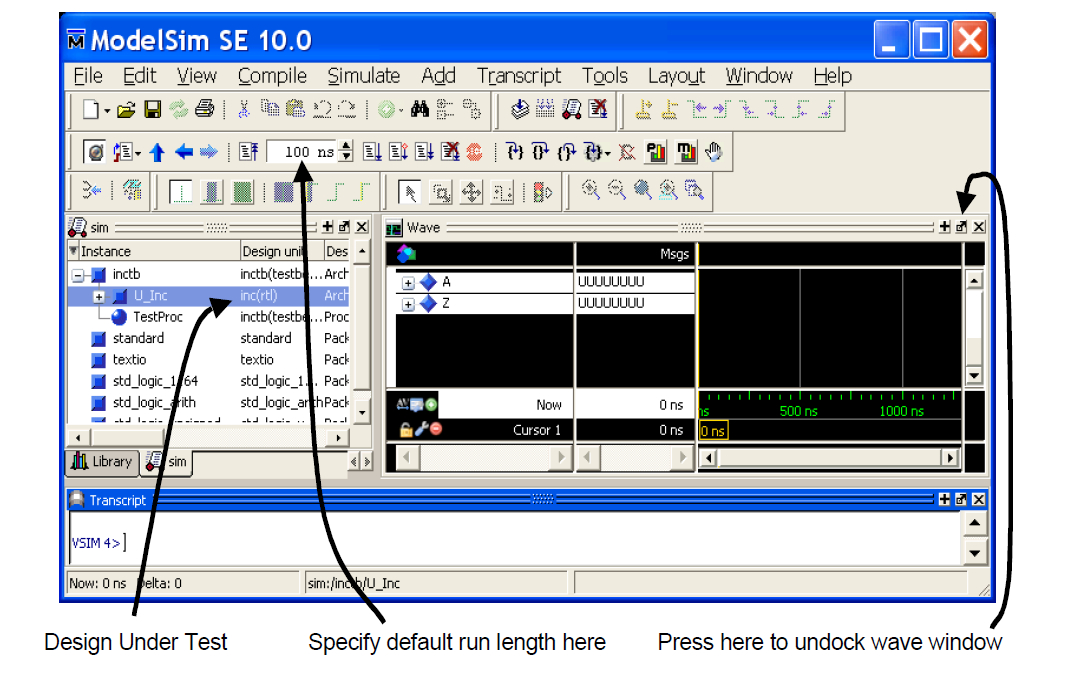

Так выглядит окно прогрмаммы QuestaSim

Слайд: Команды QuestaSim :step

- Запуск

- vsim

- Создание библиотеки

- vlib

- Компиляция кода

- vcom

- Запуск моделирования

- vsim name_run_project

- Добавление сигналов

- add wave

- Запуск исполнения и просмотр результата

- run

Слайд: Скрин каст

- Файл:Скрин каст по работе с QuestaSim.flv

- Файл:Руководство по работе с QuestaSim.pdf

- Файл:Основные команды QuestaSim.pdf