Спец курс (Избранные главы VHDL)/Лабораторные работы

Материал из Wiki

< Спец курс (Избранные главы VHDL)

Версия от 15:40, 17 октября 2012; Vidokq (обсуждение | вклад)

Это снимок страницы. Он включает старые, но не удалённые версии шаблонов и изображений.

Содержание |

Задание 1-1

- Разработать синтезируемое VHDL-описание блока кодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

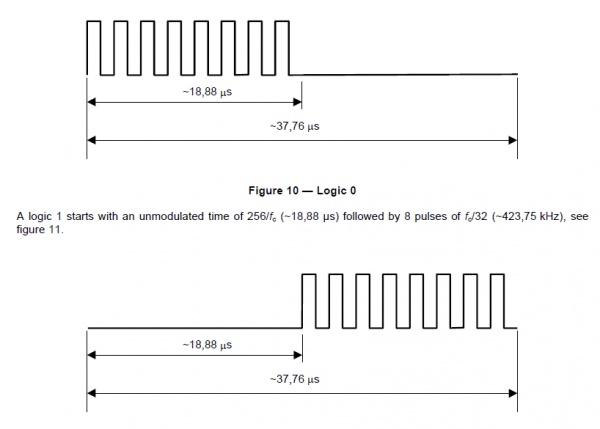

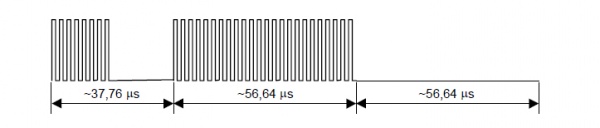

- Тип выходной кодировки 1-256 (iso-15693-2) Файл:ISO15693-2.pdf

- Частота тактового сигнала 13.56 MHz

- Перед стартом передачи данных посылать SOF

- После завершения передачи данных EOF

Задание 1-2

- Разработать синтезируемое VHDL-описание блока декодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных. (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок записи принимаемых данных в файл.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

- Тип входной кодировки 1-256 (iso-15693-2) Файл:ISO15693-2.pdf

- Частота тактового сигнала 13.56 MHz

- Прием данных начинать после получения SOF

- Прекращать прием после прихода символа EOF

Задание 2-1

- Разработать синтезируемое VHDL-описание блока кодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

- Тип выходной кодировки 1-256 (iso-15693-2) Файл:ISO15693-2.pdf

- Частота тактового сигнала 13.56 MHz

- Перед стартом передачи данных посылать SOF

- После завершения передачи данных EOF

Задание 2-2

- Разработать синтезируемое VHDL-описание блока декодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных. (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок записи принимаемых данных в файл.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

- Тип выходной кодировки 1-256 (iso-15693-2) Файл:ISO15693-2.pdf

- Частота тактового сигнала 13.56 MHz

- Перед стартом передачи данных посылать SOF

- После завершения передачи данных EOF

Задание 3-1

- Разработать синтезируемое VHDL-описание блока кодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

- Тип выходной кодировки 1-256 (iso-15693-2) Файл:ISO15693-2.pdf

- Частота тактового сигнала 13.56 MHz

- Перед стартом передачи данных посылать SOF

- После завершения передачи данных EOF

Задание 3-2

- Разработать синтезируемое VHDL-описание блока декодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных. (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок записи принимаемых данных в файл.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

- Тип входной кодировки 1-256 (iso-15693-2) Файл:ISO15693-2.pdf

- Частота тактового сигнала 13.56 MHz

- Прием данных начинать после получения SOF

- Прекращать прием после прихода символа EOF

Задание 4-1

- Разработать синтезируемое VHDL-описание блока кодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Выходной порт DATA_O, для выдачи закодированных данных

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

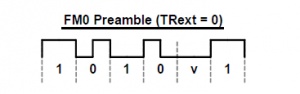

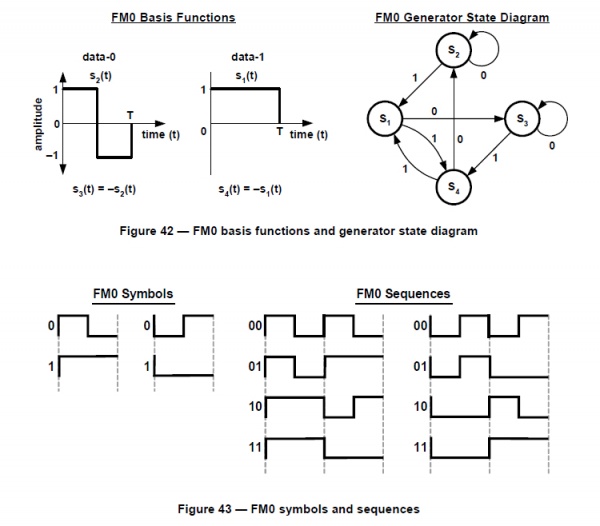

- Тип выходной кодировки FM0 (iso-18000-6) Файл:ISO18000-6REV1v62.pdf

- Число передаваемых данных задается generic паратмером NUM_SEND_BIT

- Частота тактового сигнала 1.98 MHz

- Частота закодированных данных 640 KHz

- Перед стартом передачи данных посылать SOF

- После завершения передачи данных, посылать EOF

Задание 4-2

- Разработать синтезируемое VHDL-описание блока декодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных. (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок записи принимаемых данных в файл.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

- Тип входной кодировки 1-256 (iso-18000-6) Файл:ISO18000-6REV1v62.pdf

- Число принимаемых данных задается в generic параметре NUM_GET_BIT!

- Частота тактового сигнала 1.98 MHz

- Частота закодированных данных 640 KHz

- Прием данных начинать после получения SOF

- Прекращать прием после прихода символа EOF или после получения заданного числа бит.

Задание 5-1

- Разработать синтезируемое VHDL-описание блока кодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Выходной порт DATA_O, для выдачи закодированных данных

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

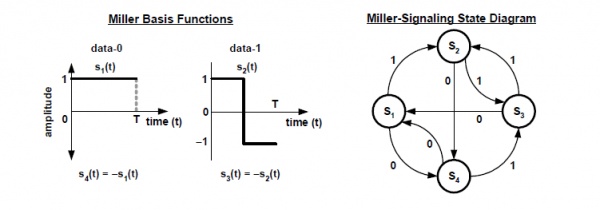

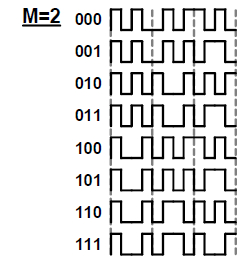

- Тип выходной кодировки код Миллера (iso-18000-6) Файл:ISO18000-6REV1v62.pdf

- Число передаваемых данных задается в generic параметре NUM_SEND_BIT !

- Частота тактового сигнала 1.98 MHz

- Частота закодированных данных 320 KHz (два такта выходной частоты на один бит данных, см. рис.)

- Перед стартом передачи данных посылать SOF

- После завершения передачи данных посылать EOF

Задание 5-2

- Разработать синтезируемое VHDL-описание блока декодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных. (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок записи принимаемых данных в файл.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Входной порт DATA_I, для принимаемых от кодера данных

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

- Тип входной кодировки код Миллера (iso-18000-6) Файл:ISO18000-6REV1v62.pdf

- Число принимаемых данных задается в generic параметре NUM_GET_BIT!

- Частота тактового сигнала 1.98 MHz

- Частота закодированных данных 320 KHz (два такта выходной частоты на один бит данных, см. рис.)

- Прием данных начинать после получения SOF

- Прекращать прием после прихода символа EOF или после приема NUM_GET_BIT

Задание 6-1

- Разработать синтезируемое VHDL-описание блока кодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Выходной порт DATA_O, для выдачи закодированных данных

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

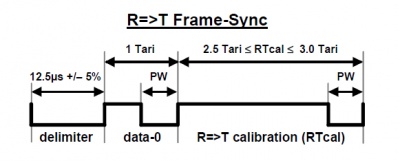

- Тип выходной кодировки iso-18000-6 Файл:Input 18000-6 (E)REV1 v62.pdf

- Число передаваемых данных задается в generic параметре NUM_SEND_BIT !

- Частота тактового сигнала 8 MHz

- Tari= 6.25us (см. рис.)

- RTcal= (Data-0) + (Data-1)=3 * Tari = 18.75us

- Перед стартом передачи данных посылать SOF

- Завершение передачи данных после посылки NUM_SEND_BIT бит данных.