ПЦУСБ/Лабораторная работа 2

- Лабораторная работа 1

- Лабораторная работа 2

- Лабораторная работа 3

Содержание |

Описание и моделирование нерегулярных логических схем

Задание

| Рисунок 1 — Пример задания схемы |

|---|

Для заданной нерегулярной логической схемы (см. пример на рисунке 1):

- составить структурное VHDL-описание;

- построить систему логических функций, реализуемую схемой и составить VHDL-описание по полученным выражениям;

- составить тестбенч для проверки эквивалентности двух VHDL-описаний, выполнив моделирование на всех наборах значений входных переменных;

- найти критический путь в схеме.

Рекомендуемый порядок выполнения работы

- Составить VHDL-модель каждого из типов элементов, входящих в схему. Если в схеме есть элементы одинакового типа, то составляется одна модель для всех элементов данного типа. Модель элемента должна учитывать задержку распространения сигнала (от входа к выходу), указанную в таблице 1. В схеме для каждого логического элемента указаны его тип (библиотечное имя) и имена входных и выходных портов.

- Составить структурную VHDL-модель схемы в целом. Предварительно следует проставить на схеме имена связей и номера элементов, которые должны соответствовать именам сигналов и меткам элементов (в операторе port map).

- По схеме составить логические уравнения зависимости выходов от входов, используя заданные в таблице 1 логические функции элементов. Составить VHDL-модель, используя полученные выражения.

- Составить тестирующую программу, включающую две VHDL-модели, и формирующую входные сигналы (полный перебор) и сравнивая ответы двух схем (сигнал OK). При сравнении ответов следует учитывать, что в структурном VHDL-описании учитываются задержки распространения сигналов в логических элементах, и поэтому правильные (окончательные) ответы со структурного и логического описаний будут разнесены во времени.

- Провести моделирование и получить временную диаграмму.

- Для каждого тестирующего набора и для каждой функции определить задержку схемы.

- Найти критический путь на схеме – путь с наибольшей суммарной задержкой элементов.

Требования к оформлению отчета

- В отчете должна быть приведена логическая схема, на которой должны быть обозначены имена сигналов и меток элементов, соответствующие описанию на языке VHDL.

- В отчете должен содержаться VHDL-код структурного (включая описания используемых библиотечных элементов) и логического описаний схемы, а также тестирующая программа.

- Описания всех элементов должны быть в отдельных файлах, при этом каждый файл должен включать следующий комментарий:

- ФИО и номер группы автора разработанной VHDL-модели;

- номер варианта;

- В отчете должны содержаться временные диаграммы, соответствующие тестирующей программе.

- В отчете должна содержаться система логических функций, реализуемых схемой.

- В отчете необходимо привести таблицу, содержащую значения задержки распространения сигналов от входа к выходам для каждого входного набора.

- На логической схеме должен быть отмечен критический путь.

- В отчете должно быть указано значение задержки схемы, соответствующее задержке критического пути.

Библиотека элементов

В таблице заданы 2 типа задержек: в относительных единицах и в пикосекундах. Относительные единицы можно приравнять к наносекундам.

| |

Группа 013201 должна использовать значения задержки в пикосекундах, |

| Имя элемента | Функция элемента | Задержка, относит. ед. |

Площадь | Задержка, пс |

|---|---|---|---|---|

| GND | 1 | — | — | |

| VCC | 1 | — | — | |

| N | 2 | 100 | 160 | |

| A2 | 4 | 1000 | 511 | |

| A3 | 5 | 1500 | 824 | |

| A4 | 6 | 400 | 1156 | |

| A6 | 10 | 400 | 1505 | |

| A8 | 12 | 400 | 2121 | |

| EX2 | 7 | 1000 | 592 | |

| MX2 | 8 | 1000 | 938 | |

| NA2 | 3 | 200 | 275 | |

| NA3 | 4 | 300 | 425 | |

| NA3O2 | 5 | 300 | 441 | |

| NA4 | 5 | 400 | 742 | |

| NAO2 | 4 | 200 | 362 | |

| NAO22 | 5 | 200 | 487 | |

| NAO3 | 5 | 300 | 1000 | |

| NAOA2 | 5 | 200 | 1000 | |

| NEX2 | 7 | 1000 | 526 | |

| NMX2 | 6 | 1000 | 593 | |

| NMX4 | 15 | 1000 | 910 | |

| NO2 | 3 | 200 | 299 | |

| NO3 | 4 | 300 | 559 | |

| NO3A2 | 5 | 300 | 643 | |

| NO4 | 5 | 400 | 1087 | |

| NOA2 | 4 | 200 | 346 | |

| NOA22 | 5 | 200 | 477 | |

| NOA3 | 5 | 300 | 570 | |

| NOAO2 | 5 | 200 | 570 | |

| O2 | 4 | 1000 | 601 | |

| O3 | 5 | 1500 | 946 | |

| O4 | 6 | 1500 | 1400 | |

| O6 | 10 | 1500 | 1831 | |

| O8 | 12 | 1500 | 2388 | |

| DFRS | D-триггер, управляемый положительным фронтом с

асинхронным сбросом и установкой с прямым выходом |

25 | 1000 | 1300 |

|

|---|

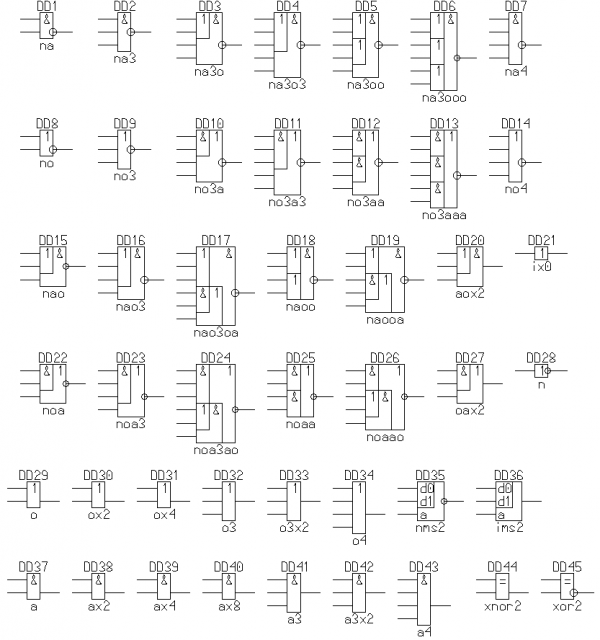

| Рисунок 1 – Условное графическое обозначение элементов |

Варианты заданий

Варианты заданий приведены в DOC-файле.

| |

Для группы 013201 вариант задания соответствует номеру в журнале. |

Шпаргалка

| |

|---|

| Схема |

1. На схеме подписываются все связи и даются имена всем элементам. Подписывать элементы рекомендуется как принято в ГОСТе: слева направо, сверху вниз. Рекомендуется использовать префикс DD в метке элемента.

2. Определяется список библиотечных элементов, входящих в схему.

| Имя элемента | Функция элемента | Задержка, относит. ед. |

Площадь | Задержка, пс |

|---|---|---|---|---|

| N | 2 | 100 | 160 | |

| NA3 | 4 | 300 | 425 | |

| NO2 | 3 | 200 | 299 | |

| NAO22 | 5 | 200 | 487 | |

| NOAO2 | 5 | 200 | 570 |

По функциям заданным в таблице составляются соответствующие VHDL описания используемых логических элементов. Для примера будем использовать задержки заданные в условных единицах, которые приравняем к наносекундам (т.е. значения заданные в таблице домножим на 1 нс).

| Файл: N.vhd |

ibrary ieee; use ieee.std_logic_1164.all; entity n is generic ( del : time := 2 ns); port ( A : in std_logic; Y : out std_logic); end entity n; architecture beh of n is begin -- architecture beh Y <= not A after del; end architecture beh; |

| Файл: NO2.vhd |

library ieee; use ieee.std_logic_1164.all; entity NO2 is port ( A, B : in std_logic; Y : out std_logic); end entity NO2; architecture beh of NO2 is begin -- architecture beh Y <= not (A or B) after 3 ns; end architecture beh; |

| Файл: NA3.vhd |

library ieee; use ieee.std_logic_1164.all; entity NA3 is generic ( del : time := 4 ns); port ( A : in std_logic; B : in std_logic; C : in std_logic; Y : out std_logic); end entity NA3; architecture beh of NA3 is begin -- architecture beh Y <= not (A and B and C) after del; end architecture beh; |

| Файл: NAO22.vhd |

library ieee; use ieee.std_logic_1164.all; entity NAO22 is generic ( del : time := 5 ns); port ( A : in std_logic; B : in std_logic; C : in std_logic; D : in std_logic; Y : out std_logic); end entity NAO22; architecture beh of NAO22 is begin Y <= not ((A or B) and (C or D)) after del; end architecture beh; |

| Файл: NOAO2.vhd |

library ieee; use ieee.std_logic_1164.all; entity NOAO2 is generic ( -- del : time := 570 ps); del : time := 5 ns); port ( A : in std_logic; B : in std_logic; C : in std_logic; D : in std_logic; Y : out std_logic); end entity NOAO2; architecture beh of NOAO2 is begin Y <= not (A or (B and (C or D))) after del; end architecture beh; |

| Файл: lib_p.vhd |

------------------------------------------------------------------------------- -- Project : Lab02 -- Variant : 01 -- Author : ANA (XXX group) ------------------------------------------------------------------------------- library ieee; use ieee.std_logic_1164.all; package lib is component n is generic ( del : time := 2 ns); port ( A : in std_logic; Y : out std_logic); end component n; component NO2 is port ( A, B : in std_logic; Y : out std_logic); end component NO2; component NA3 is -- generic ( -- del : time :); port ( A : in std_logic; B : in std_logic; C : in std_logic; Y : out std_logic); end component NA3; component NAO22 is generic ( del : time := 5 ns); port ( A : in std_logic; B : in std_logic; C : in std_logic; D : in std_logic; Y : out std_logic); end component NAO22; component NOAO2 is generic ( del : time := 5 ns); port ( A : in std_logic; B : in std_logic; C : in std_logic; D : in std_logic; Y : out std_logic); end component NOAO2; end package lib; |

| Файл: sch01.vhd |

------------------------------------------------------------------------------- -- Project : Lab02 -- Variant : 01 -- Author : ANA (XXX group) ------------------------------------------------------------------------------- library ieee; use ieee.std_logic_1164.all; use work.lib.all; entity sch01 is port ( X : in std_logic_vector(3 downto 1); Y : out std_logic_vector(2 downto 1)); end entity sch01; architecture sch of sch01 is signal x1_n, x2_n, x3_n : std_logic; signal DD3_Y : std_logic; signal DD4_Y : std_logic; signal DD5_Y : std_logic; signal DD5_YN : std_logic; signal DD8_Y : std_logic; begin DD1: n port map (X(1), X1_N); DD2: n port map (A => X(2), Y => X2_N); DD3: NO2 port map ( A => X1_N, B => X(2), Y => DD3_Y); DD4: NO2 port map (X(1), X(3), DD4_Y); DD5: NA3 port map ( A => x2_N, B => X(1), C => x(3), Y => DD5_Y); DD6: n port map (DD5_Y, DD5_YN); DD7: n port map (X(3), X3_N); DD8: NA3 port map ( A => x(1), B => DD4_Y, C => x(3), Y => DD8_Y); DD9: NAO22 port map ( A => DD3_Y, B => DD4_Y, C => DD8_Y, D => DD5_YN, Y => Y(1)); DD10: NOAO2 port map ( A => X(1), B => X3_N, C => DD3_Y, D => DD5_Y, Y => Y(2)); end architecture sch; |

| Файл: sch01_log.vhd |

------------------------------------------------------------------------------- -- Project : Lab02 -- Variant : 01 -- Author : ANA (XXX group) ------------------------------------------------------------------------------- library ieee; use ieee.std_logic_1164.all; use work.lib.all; entity sch01a is port ( X : in std_logic_vector(3 downto 1); Y : out std_logic_vector(2 downto 1)); end entity sch01a; architecture log of sch01a is signal DD3_Y : std_logic; signal DD4_Y : std_logic; signal DD5_Y : std_logic; signal DD8_Y : std_logic; begin -- DD3: NO2 DD3_Y <= not ( not X(1) or X(2) ); -- DD4: NO2 DD4_Y <= not ( X(1) or X(3) ); -- DD5: NA3 DD5_Y <= not ( not x(2) and X(1) and x(3) ); -- DD8: NA3 DD8_Y <= not (x(1) and DD4_Y and x(3)); -- DD9: NAO22 Y(1) <= not ((DD3_Y or DD4_Y) and (DD8_Y or not DD5_Y)); -- DD10: NOAO2 Y(2) <= not (X(1) or (not x(3) and (DD3_Y or DD5_Y))); end architecture log; |

| Файл: sch01_tb.vhd |

------------------------------------------------------------------------------- -- Project : Lab02 -- Variant : 01 -- Author : ANA (XXX group) ------------------------------------------------------------------------------- library ieee; use ieee.std_logic_1164.all; entity sch01_tb is end entity sch01_tb; architecture tb of sch01_tb is -- components component sch01 is port ( X : in std_logic_vector(3 downto 1); Y : out std_logic_vector(2 downto 1)); end component sch01; component sch01a is port ( X : in std_logic_vector(3 downto 1); Y : out std_logic_vector(2 downto 1)); end component sch01a; signal X : std_logic_vector(2 downto 0) := (others => '0'); signal Y1 : std_logic_vector(2 downto 1); signal Y2 : std_logic_vector(2 downto 1); signal OK : std_logic; begin DUT1: sch01 port map ( X => X, Y => Y1); DUT2: sch01a port map ( X => X, Y => Y2); x(0) <= not x(0) after 50 ns; x(1) <= not x(1) after 100 ns; x(2) <= not x(2) after 200 ns; OK <= '1' when Y1 = Y2 else 'X'; end architecture tb; |