< Спец курс (Избранные главы VHDL)

Это снимок страницы. Он включает старые, но не удалённые версии шаблонов и изображений.

Лекции

Практические

Лабораторные

Табель

Доп. материалы

- Заголовок

- Критерий качества схемы

- Автор

- Зайцев В.С.

- Нижний колонтитул

- Спец курс (Избранные главы VHDL)/Критерий качества схемы

- Дополнительный нижний колонтитул

- Зайцев В.С., 13:13, 2 декабря 2013

Слайд:Снижение энерго-потребления схем

| Способы сокращения потребления

|

Определение

|

Оптимизация дерева синхронизации

Clock tree optimization and clock gating

|

Отключаются ветви дерева синхронизации, которые не используются в данный момент времени.

|

| Операция изоляции Operand isolation

|

Уменьшается рассеиваемая мощность, путем использования разрешающего сигнала, если разрешающий сигнал не активен, то переключение блока не произойдет.

|

| Логическое деление блоков Logic restructuring

|

Разделение логики на блоки, работающие на высокой частоте и на низкой, на сколько это возможно.

|

| Изменение размеров транзисторов Logic resizing (transistor resizing)

|

Уменьшается динамический ток потребления (входные и выходные паразитные емкости), а так же токи утечки при переключении (сквозные токи).

|

| Использование буферов Transition rate buffering

|

Снижает мощность переключения путем уменьшения времени переключения.

|

| Замена точек подключения Pin swapping

|

Выбираются точки подключения с минимальной емкостной нагрузкой.

|

| Использование разных порогов Multi-Vth

|

Использование нескольких библиотек с разными характеристиками транзисторов (с низким порогом переключения – быстрее и выше утечки) или с более высокими – медленнее с более низкими утечками.

|

| Несколько напряжений питания в схеме Multi-supply voltage (MSV or voltage islands)

|

Функциональные блоки работают при различных напряжения питания.

|

| Динамическое изменение напряжения питания (DVS) Dynamic voltage scaling (DVS)

|

Позволяет менять напряжение питания блока во время работы схемы на лету.

|

| Динамическое изменение напряжения и частоты (DVFS) Dynamic voltage and frequency scaling (DVFS)

|

Позволяет менять напряжение питания и частоту блока во время работы схемы на лету.

|

| Адаптивное изменение напряжения и частоты Adaptive voltage and frequency scaling (AVFS)

|

In this variation of DVFS, a wider variety of voltages are set dynamically, based on adaptive feedback from a control loop; involves analog circuitry.

|

| Отключение питания (PSO) Power shut-off (PSO) [or power gating]

|

Отключение питания блоков, если он не используется.

|

| Разделение памяти Memory splitting

|

Если данные постоянные в одной области памяти и перезаписываются в другой, то целесообразно разделить области и отключать питание той области, где данные не изменяются.

|

| Смещение питания Substrate biasing (bodybiasing or back-biasing)

|

Смещение напряжения на кармане p-транзисторов выше VDD и подложки n-транзисторов ниже VSS.

|

Слайд:Снижение энерго-потребления схем (2)

|

|

Dynamic Power Savings

|

Leakage Power Savings

|

Timing Penalty

|

Area Penalty

|

Complexity and Time-to-Market (TTM) Penalties

|

Implementation Impact

|

Design Impact

|

Verification Impact

|

| Dynamic power reduction techniques

|

| Clock gating |

20% |

~0X

|

~0%

Clock tree insertion delay

|

<2% |

None |

Low |

Low |

None

|

| Operand isolation |

<5% |

~0X

|

~0% May add a few gates to pipeline

|

|

None |

None |

None |

None

|

| Logic restructuring

|

<5% |

~0X |

~0% |

Little |

None |

None |

None |

None

|

| Logic resizing

|

<5% |

~0X |

~0% |

~0% to –10% |

None |

None |

None |

None

|

| Transition rate buffering

|

<5% |

~0X |

~0% |

Little |

None |

None |

None |

None

|

| Pin swapping

|

<5% |

~0X |

~0% |

Little |

None |

None |

None |

None

|

| Leakage power reduction techniques

|

| Multi-Vth

|

0% |

2–3X |

~0% Automated |

2 to –2% |

Low |

Low |

None |

None

|

| Multisupply voltage (MSV)

|

40–50% |

2X

|

~0% Adds level shifters; clock scheduling issues due to latency changes

|

<10% Power routing and power interconnect; level shifters

|

High Design time, turnaround time, TTM

|

Medium |

Medium |

Low

|

| DVFS |

40–70% |

2–3X

|

~0% Adds level shifters, power-up sequence; clock scheduling issues due to dynamic latency changes

|

<10% Adds level shifters and a power management unit

|

High Design time, turnaround time, TTM

|

High |

High |

High

|

| Power shut-off (PSO)

|

~0% |

10–50X

|

4–8% Adds isolation cells, complex timing, wakeup time, rush currents

|

5–15% Adds isolation cells, state retention cells, alwayson cells; may have wider power grid due to rush currents; power management unit

|

High System architecture, support for power control, verification, synthesis, implementation, DFT

|

Mediumhigh |

High |

High

|

| Memory splitting

|

~0% |

Varies |

Varies Adds isolation cells for power shut-off

|

Varies |

Varies |

Mediumhigh |

High |

High

|

| Substrate biasing

|

~0% |

10X |

10% |

<10% |

High |

High |

Mediumhigh |

Medium

|

Пример VHDL

Слайд: Операция изоляции

Сравнение происходит постоянно по каждому такту

library ieee, std, djin18;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

architecture beh of xcontroller is

signal count : unsigned (7 downto 0);

signal do_i : std_logic;

begin -- beh

process (clk, rst)

begin

if rst = '1' then

count <= x"00";

elsif clk'event and clk = '1' then

count <= count + 1;

end if;

end process;

DO_i <= '1' when count > x"0F" else

'0';

do <= do_i when en = '1' else

'0';

end beh; Сравнение происходит только, когда требуется

architecture beh2 of xcontroller is

signal count : unsigned (7 downto 0);

signal count_i : unsigned (7 downto 0);

signal do_i : std_logic;

begin -- beh

process (clk, rst)

begin

if rst = '1' then

count <= x"00";

elsif clk'event and clk = '1' then

count <= count + 1;

end if;

end process;

count_i <= count when en = '1' else

x"00";

DO_i <= '1' when count_i > x"0F" else

'0';

do <= do_i when en = '1' else

'0';

end beh2; Слайд: Логическое деление блоков

Обработка происходит каждый такт

library ieee, std, djin18;

architecture beh4 of xcontroller is

signal count : unsigned (7 downto 0);

signal count2 : unsigned (7 downto 0);

begin

process (clk, rst)

begin

if rst = '0' then

count <= x"00";

count2 <= x"00";

elsif clk'event and clk = '1' then

count <= count + 1;

if count = 10 then

count2 <= count2 + 1;

end if;

end if;

end process;

dbuso <= std_logic_vector(count2);

end beh4; Формируется строб обработки

architecture beh of xcontroller is

signal count : unsigned (7 downto 0);

signal count2 : unsigned (7 downto 0);

signal strob : std_logic;

begin

process (clk, rst)

begin

if rst = '0' then

count <= x"00";

strob <= '0';

elsif clk'event and clk = '1' then

count <= count + 1;

if count = 10 then

strob <= '1';

else

strob <= '0';

end if;

end if;

end process;

process (strob, rst)

begin

if rst = '0' then

count2 <= x"00";

elsif strob'event and strob = '1' then

count2 <= count2 + 1;

end if;

end process;

dbuso <= std_logic_vector(count2);

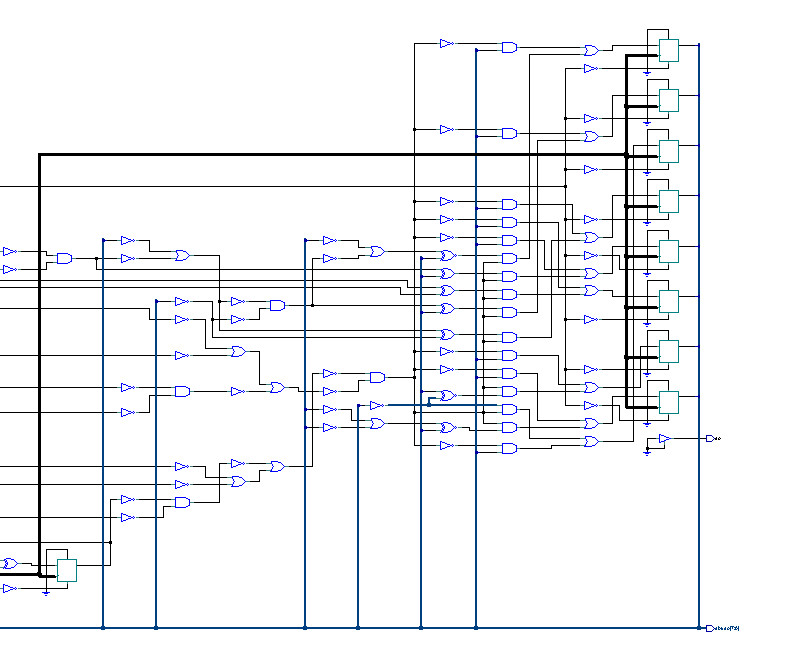

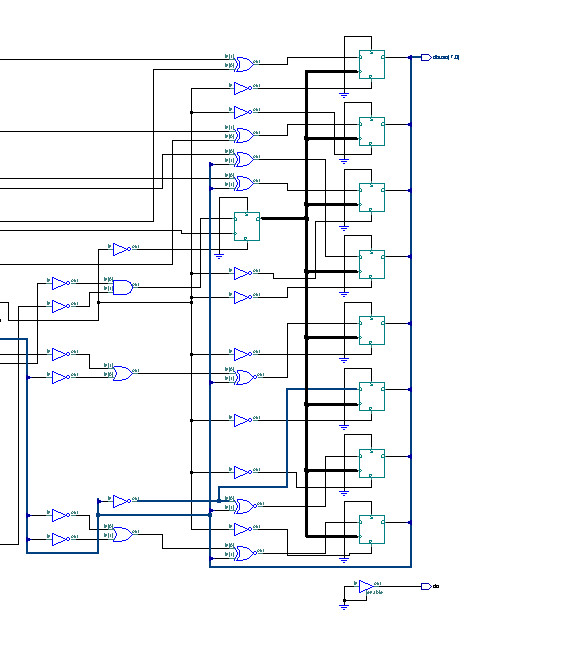

end beh; Слайд: Логическое деление блоков (рис)

Тактовый сигнал VS все тригеры

Строб управления VS все тригеры

Площадь схем кристалла

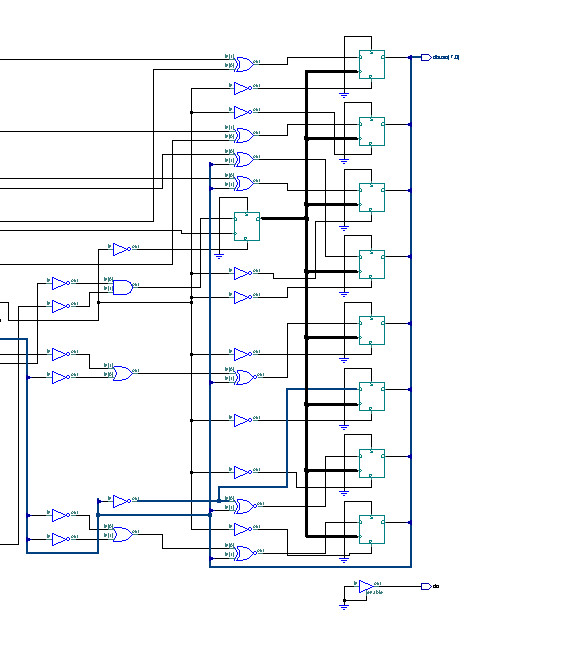

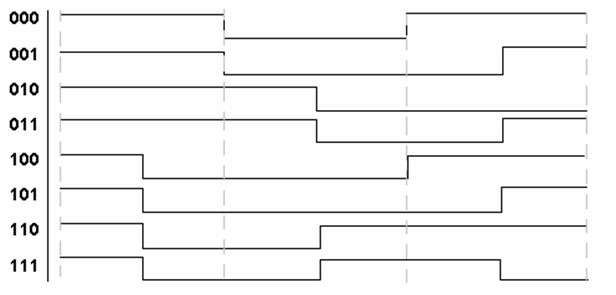

Слайд: Алгоритм кодирования миллера

Граф переходов, описывающий алгоритм получения кода Миллера

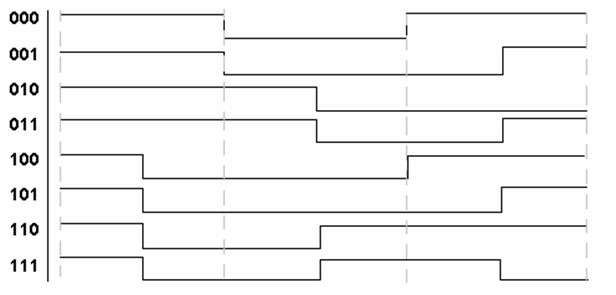

Возможные наборы переключений кода Миллера

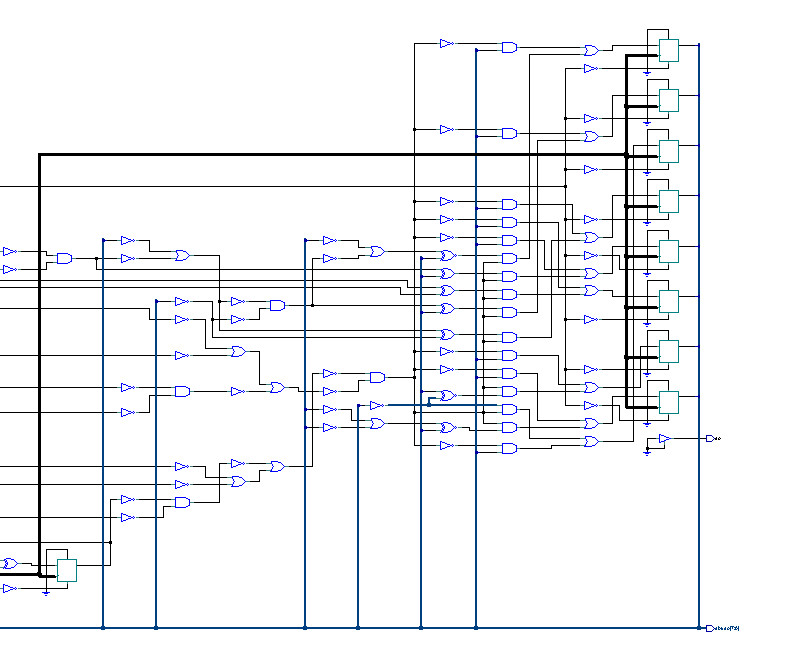

Слайд: Различные описания блока кодирования RFID

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.NUMERIC_STD.ALL;

ARCHITECTURE BEH1 OF MILLER IS

SIGNAL OUTPUT_DATAI : STD_LOGIC;

SIGNAL OUTPUT_DATAII : STD_LOGIC;

TYPE ST IS (a1,a2,a3,a4);

SIGNAL STATE , STATEI : ST;

signal input_data_i : std_logic;

begin

input_data_i <= input_data;

coder_proc: process (clk_i_d, rst)

begin -- process coder_proc

if rst = '1' then

state <= a1;

elsif clk_i_d'event and clk_i_d = '0' then

state <= statei;

end if;

end process coder_proc;acincro: process (state,statei,input_data_i)

begin -- process acincro

case state is

when a1 =>

if input_data_i = '0' then

statei <= a2;

else

statei <= a4;

end if;

when a2 =>

if input_data_i = '0' then

statei <= a3;

else

statei <= a4;

end if;

when a3 =>

if input_data_i = '0' then

statei <= a2;

else

statei <= a1;

end if;

when others =>

if input_data_i = '0' then

statei <= a3;

else

statei <= a1;

end if;

end case;

end process acincro; |

suncrodata: process (state,input_data_i,clk_i_d)

begin -- process suncrodata

case STATE is

when a1 =>

if input_data_i = '0' then

output_datai <= not clk_i_d;

else

output_datai <= '0';

end if;

when a2 =>

if input_data_i = '0' then

output_datai <= clk_i_d;

else

output_datai <= '0';

end if;

when a3 =>

if input_data_i = '0' then

output_datai <= not clk_i_d;

else

output_datai <= '1';

end if;

when others =>

if input_data_i = '0' then

output_datai <= clk_i_d;

else

output_datai <= '1';

end if;

end case;

end process suncrodata;

syn_out: process (clk, rst)

begin -- process syn_out

if rst = '1' then

output_data <= '1';

elsif clk'event and clk = '1' then

output_data <= output_datai;

end if;

end process syn_out;

end beh1; |

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.NUMERIC_STD.ALL;

ARCHITECTURE BEH3 OF MILLER IS

TYPE ST IS (a1,a2,a3,a4);

SIGNAL STATE , STATEI : ST;

SIGNAL OUTPUT_DATAI : STD_LOGIC;

SIGNAL OUTPUT_DATAIi : STD_LOGIC;

signal input_data_i : std_logic;

begin

input_data_i <= input_data;

coder_proc: process (clk_i_d, rst)

begin -- process coder_proc

if rst = '1' then

state <= a1;

elsif clk_i_d'event and clk_i_d = '0' then

state <= statei;

end if;

end process coder_proc;statei <=

a1 when input_data = '1' and (state = a4 or state = a3) else

a2 when input_data = '0' and (state = a1 or state = a3) else

a3 when input_data = '0' and (state = a2 or state = a4) else

a4;

output_datai <=

'1' when statei = a1 else

not clk_i_d when statei = a2 else

clk_i_d when statei = a3 else

'0';

suncrodata: process (clk, rst)

begin -- process suncrodata

if rst = '1' then

output_data <= '1';

elsif clk'event and clk = '1' then

output_data <= output_datai;

end if;

end process suncrodata;

end beh3; |

architecture beh4 of miller is

signal input_data_i : std_logic;

signal syn_input_data_i : std_logic;

signal output_data_i : std_logic;

signal output_data_ii : std_logic;

--signal output_data_iii : std_logic;

signal syn_output_data_i : std_logic;

begin -- beh4

input_data_i <= input_data;

coder_proc: process (clk_i_d, rst)

begin -- process coder_proc

if rst = '1' then

syn_input_data_i <= '0';

elsif clk_i_d'event and clk_i_d = '1' then

syn_input_data_i <= input_data_i;

end if;

end process coder_proc;

pre_code_data: process (clk_i_d, rst)

begin -- process pre_code_data

if rst = '1' then

syn_output_data_i <= '1';

elsif clk_i_d'event and clk_i_d = '1' then

syn_output_data_i <= output_data_i;

end if;

end process pre_code_data; |

output_data_ii <=

(not clk_i_d) xor syn_output_data_i when input_data_i = '1' else

(not syn_output_data_i) xor syn_input_data_i;

output_signal_code_proc: process (clk, rst)

begin -- process output_signal_code_proc

if rst = '1' then

output_data_i <= '1';

elsif clk'event and clk = '1' then

output_data_i <= output_data_ii;

end if;

end process output_signal_code_proc;

output_data <= output_data_i;

end beh4; |

architecture beh5 of miller is

signal input_data_i : std_logic;

signal syn_input_data_i : std_logic;

signal output_data_i : std_logic;

signal output_data_ii : std_logic;

signal output_data_iii : std_logic;

signal syn_output_data_i : std_logic;

begin -- beh4

input_data_i <= input_data;

coder_proc: process (clk_i_d, rst)

begin -- process coder_proc

if rst = '1' then

syn_input_data_i <= '0';

elsif clk_i_d'event and clk_i_d = '1' then

syn_input_data_i <= input_data_i;

end if;

end process coder_proc;

pre_code_data: process (clk_i_d, rst)

begin -- process pre_code_data

if rst = '1' then

syn_output_data_i <= '1';

elsif clk_i_d'event and clk_i_d = '1' then

syn_output_data_i <= output_data_i;

end if;

end process pre_code_data; |

output_signal_code_proc: process (clk, rst)

begin -- process output_signal_code_proc

if rst = '1' then

output_data_i <= '1';

elsif clk'event and clk = '1' then

if input_data_i = '1' then

if syn_input_data_i = '1' then

if syn_output_data_i = '1' then

output_data_i <= clk_i_d;

else

output_data_i <= not clk_i_d;

end if;

else

if syn_output_data_i = '1' then

output_data_i <= clk_i_d;

else

output_data_i <= not clk_i_d;

end if;

end if;

else

if syn_input_data_i = '1' then

if syn_output_data_i = '1' then

output_data_i <= '1';

else

output_data_i <= '0';

end if;

else

if syn_output_data_i = '1' then

output_data_i <= '0';

else

output_data_i <= '1';

end if;

end if;

end if;

end if;

end process output_signal_code_proc;

output_data <= output_data_i;

end beh5; |

Слайд: Результаты синтеза конечного автомата

set encoding binary;

Encodings for ST values

value ST[1-0]

========================

a1 00

a2 01

a3 10

a4 11

...................

*******************************************************

Cell: fm0_miller View: beh2 Library: digital

*******************************************************

Cell Library References Total Area

fdr alib5 2 x 322 645 um_2

fds alib5 1 x 342 342 um_2

n alib5 3 x 31 94 um_2

na alib5 2 x 51 101 um_2

nao alib5 5 x 73 364 um_2

xnor2 alib5 1 x 100 100 um_2

Number of ports : 6

Number of nets : 19

Number of instances : 14

Number of references to this view : 0

Total accumulated area :

Number of um_2 : 1647

Number of accumulated instances : 14set encoding auto;

Encodings for ST values

value ST[1-0]

========================

a1 00

a2 01

a3 10

a4 11

*******************************************************

Cell: fm0_miller View: beh2 Library: digital

*******************************************************

Cell Library References Total Area

fdr alib5 2 x 322 645 um_2

fds alib5 1 x 342 342 um_2

n alib5 3 x 31 94 um_2

na alib5 2 x 51 101 um_2

nao alib5 5 x 73 364 um_2

xnor2 alib5 1 x 100 100 um_2

Number of ports : 6

Number of nets : 19

Number of instances : 14

Number of references to this view : 0

Total accumulated area :

Number of um_2 : 1647

Number of accumulated instances : 14set encoding grey;

Encodings for ST values

value ST[1-0]

========================

a1 00

a2 01

a3 11

a4 10

*******************************************************

Cell: fm0_miller View: beh2 Library: digital

*******************************************************

Cell Library References Total Area

fdr alib5 2 x 322 645 um_2

fds alib5 1 x 342 342 um_2

n alib5 2 x 31 63 um_2

na alib5 3 x 51 152 um_2

nao alib5 2 x 73 146 um_2

no alib5 1 x 52 52 um_2

no3a alib5 1 x 93 93 um_2

xnor2 alib5 1 x 100 100 um_2

xor2 alib5 1 x 108 108 um_2

Number of ports : 6

Number of nets : 19

Number of instances : 14

Number of references to this view : 0

Total accumulated area :

Number of um_2 : 1702

Number of accumulated instances : 14 Слайд: Быстродействие

set encoding binary;

Clock Frequency Report

Clock : Frequency

===============================================================================

clk_i_d : 287.4 MHz

clk : 310.3 MHz

Critical Path Report

Critical path #1, (path slack = 66.7):

NAME GATE ARRIVAL LOAD

================================================================================

rst/ 0.00 0.00 up 0.11

reg_STATE(0)_ix1_ix1_ix1/q fdr 1.28 1.28 up 0.07

ix442/y n 0.22 1.50 dn 0.04

ix444/y na 0.25 1.76 up 0.02

ix23/y na3o 0.59 2.35 dn 0.04

ix11/y nao 0.26 2.61 up 0.02

reg_STATE(0)_ix1_ix1_ix1/d fdr 0.00 2.61 up 0.00

data arrival time 2.61

data required time 69.30

================================================================================

data required time 69.30

data arrival time 2.61

==========

slack 66.69

================================================================================set encoding auto;

Clock Frequency Report

Clock : Frequency

=====================================

clk_i_d : 287.4 MHz

clk : 310.3 MHz

Critical Path Report

Critical path #1, (path slack = 66.7):

NAME GATE ARRIVAL LOAD

================================================================================

rst/ 0.00 0.00 up 0.11

reg_STATE(0)_ix1_ix1_ix1/q fdr 1.28 1.28 up 0.07

ix442/y n 0.22 1.50 dn 0.04

ix444/y na 0.25 1.76 up 0.02

ix23/y na3o 0.59 2.35 dn 0.04

ix11/y nao 0.26 2.61 up 0.02

reg_STATE(0)_ix1_ix1_ix1/d fdr 0.00 2.61 up 0.00

data arrival time 2.61

data required time 69.30

================================================================================

data required time 69.30

data arrival time 2.61

==========

slack 66.69

================================================================================ set encoding grey;

Clock Frequency Report

Clock : Frequency

====================================

clk_i_d : 238.9 MHz

clk : 277.7 MHz

Critical Path Report

Critical path #1, (path slack = 66.0):

NAME GATE ARRIVAL LOAD

=================================================================================

rst/ 0.00 0.00 up 0.11

ix455/q fdr 1.33 1.33 up 0.09

ix23/y xnor2 0.77 2.10 up 0.07

ix477/y na 0.34 2.44 dn 0.02

ix17/y nao 0.26 2.70 up 0.02

ix474/y na 0.35 3.05 dn 0.02

ix453/y nao 0.26 3.31 up 0.02

ix455/d fdr 0.00 3.31 up 0.00

data arrival time 3.31

data required time 69.30

================================================================================

data required time 69.30

data arrival time 3.31

===========

slack 65.99

=================================================================================