Open Source VHDL Verification Methodology/Пример использования OS-VVM

Материал из Wiki

Проект OS-VVM

Исходные коды

- Пример использования OS-VVM

Презентации

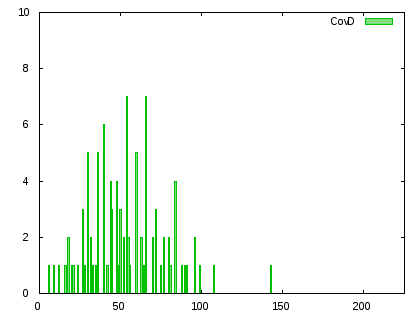

Coverage

Содержание |

Листинги

Листинг файла tstb(BEHAVIOR)

| Файл: tstb.vhd |

library ieee; use ieee.std_logic_1164.all; use ieee.math_real.all; use ieee.numeric_std.all; entity tstb is end; architecture BEHAVIOR of tstb is component sxema port (a, b : in std_logic_vector (4 downto 1); d : out std_logic_vector (8 downto 1)); end component; signal a, b : std_logic_vector (4 downto 1); signal d : std_logic_vector (8 downto 1); begin p0 : sxema port map ( a => a, b => b, d => d); RandomGenProc1 : process variable RandomVal_1, RandomVal_2 : real; -- Random value variable DataSent_1, DataSent_2 : integer; variable seed1_a : positive := 7; -- initialize seeds variable seed2_a : positive := 1; variable seed1_b : positive := 4; -- initialize seeds variable seed2_b : positive := 2; begin for i in 1 to 100 loop uniform(seed1_a, seed2_a, RandomVal_1); -- randomize 0.0 to 1.0 uniform(seed1_b, seed2_b, RandomVal_2); -- randomize 0.0 to 1.0 DataSent_1 := integer(trunc(RandomVal_1*15.0)); -- scale to 0 to 15 DataSent_2 := integer(trunc(RandomVal_2*15.0)); -- scale to 0 to 15 a <= std_logic_vector(to_unsigned(DataSent_1, 4)); b <= std_logic_vector(to_unsigned(DataSent_2, 4)); wait for 50 ns; end loop; wait ; end process; end; |

Листинг файла tstb(tb)

Листинг файла tstb.vhd

| Файл: tstb.vhd |

------------------------------------------------------------------------------- library ieee; use ieee.std_logic_1164.all; use ieee.math_real.all; use ieee.numeric_std.all; use work.RandomPkg.all; use work.CoveragePkg.all; architecture tb of tstb is component sxema port (a, b : in std_logic_vector (4 downto 1); d : out std_logic_vector (8 downto 1)); end component; signal a, b : std_logic_vector (4 downto 1); signal d : std_logic_vector (8 downto 1); shared variable RndA, RndB : RandomPType; shared variable CovA, CovB, CovD : CovPType ; begin p0 : sxema port map ( a => a, b => b, d => d); RandomGenProc1 : process -- variable RndVal1, RndVal_2 : real; -- Random value -- variable DataSent1, DataSent2 : integer; variable SeedA1 : positive := 7; -- initialize seeds variable SeedA2 : positive := 1; variable SeedB1 : positive := 4; -- initialize seeds variable SeedB2 : positive := 2; begin -- инициализация генератора псевдослучайных чисел RndA.InitSeed(IV => (SeedA1,SeedA2)); RndB.InitSeed(IV => (SeedB1,SeedB2)); RndA.SetRandomParm ( Distribution => NORMAL, Mean => 5.0, Deviation => 2.0 ) ; RndB.SetRandomParm ( Distribution => NORMAL, Mean => 10.0, Deviation => 2.0 ) ; -- создание корзин для a, b, d CovA.AddBins(GenBin(0,15)); CovB.AddBins(GenBin(0,15)); CovD.AddBins(GenBin(0,225)); for i in 1 to 100 loop a <= RndA.RandSlv(0,15,4); b <= RndB.RandSlv(0,15,4); --a <= std_logic_vector(to_unsigned(DataSent_1, 4)); --b <= std_logic_vector(to_unsigned(DataSent_2, 4)); wait for 10 ns; CovA.ICover(to_integer(unsigned(a))); CovB.ICover(to_integer(unsigned(b))); CovD.ICover(to_integer(unsigned(d))); end loop; CovA.WriteBin; CovB.WriteBin; CovD.WriteBin; -- CovA.DumpBin; -- CovA.WriteOrderCount; CovA.WriteCovDb ("CovA.db", OpenKind => WRITE_MODE ); CovB.WriteCovDb ("CovB.db", OpenKind => WRITE_MODE ); CovD.WriteCovDb ("CovD.db", OpenKind => WRITE_MODE ); wait ; end process; end architecture tb; |

Листинг файла tstb(tb2)

Случайным образом генерит числа A и B до тех пор пока не переберёт все возможные входные значения требуется 102 цикла генерации

Листинг файла tstb_tb2.vhd

| Файл: tstb_tb2.vhd |

-- Случайным образом генерит числа A и B до тех пор пока не переберёт -- все возможные входные значения -- требуется 102 цикла генерации library ieee; use ieee.std_logic_1164.all; use ieee.math_real.all; use ieee.numeric_std.all; use work.RandomPkg.all; use work.CoveragePkg.all; architecture tb2 of tstb is component sxema port (a, b : in std_logic_vector (4 downto 1); d : out std_logic_vector (8 downto 1)); end component; signal a, b : std_logic_vector (4 downto 1); signal d : std_logic_vector (8 downto 1); shared variable RndA, RndB : RandomPType; shared variable CovA, CovB, CovD : CovPType ; begin p0 : sxema port map ( a => a, b => b, d => d); RandomGenProc1 : process -- variable RndVal1, RndVal_2 : real; -- Random value -- variable DataSent1, DataSent2 : integer; variable SeedA1 : positive := 7; -- initialize seeds variable SeedA2 : positive := 1; variable SeedB1 : positive := 4; -- initialize seeds variable SeedB2 : positive := 2; variable i : natural := 0; begin -- инициализация генератора псевдослучайных чисел RndA.InitSeed(IV => (SeedA1,SeedA2)); RndB.InitSeed(IV => (SeedB1,SeedB2)); -- RndA.SetRandomParm ( -- Distribution => NORMAL, -- Mean => 5.0, -- Deviation => 2.0 ) ; -- RndB.SetRandomParm ( -- Distribution => NORMAL, -- Mean => 10.0, -- Deviation => 2.0 ) ; -- создание корзин для a, b, d CovA.AddBins(GenBin(0,15)); CovB.AddBins(GenBin(0,15)); CovD.AddBins(GenBin(0,225)); MainCovLoop: while not (CovA.IsCovered and CovB.IsCovered) loop -- MainCovLoop: while not (CovD.IsCovered) loop a <= RndA.RandSlv(0,15,4); b <= RndB.RandSlv(0,15,4); --a <= std_logic_vector(to_unsigned(DataSent_1, 4)); --b <= std_logic_vector(to_unsigned(DataSent_2, 4)); wait for 10 ns; CovA.ICover(to_integer(unsigned(a))); CovB.ICover(to_integer(unsigned(b))); CovD.ICover(to_integer(unsigned(d))); i := i+1; if i=1000000 then exit; end if; end loop; CovA.WriteBin; CovB.WriteBin; CovD.WriteBin; -- CovA.DumpBin; -- CovA.WriteOrderCount; CovA.WriteCovDb ("CovA.db", OpenKind => WRITE_MODE ); CovB.WriteCovDb ("CovB.db", OpenKind => WRITE_MODE ); CovD.WriteCovDb ("CovD.db", OpenKind => WRITE_MODE ); wait ; end process; end architecture tb2; |

Листинг файла tstb(tb3)

Случайным образом генерит входные A и B с помощью пакета покрытия т.е. интеллектуальный тестбенч Для покрытия всех состояний требуется 16 циклов

Листинг файла tstb_tb3.vhd

| Файл: tstb_tb3.vhd |

-- Случайным образом генерит входные A и B с помощью пакета покрытия -- т.е. интеллектуальный тестбенч -- Для покрытия всех состояний требуется 16 циклов library ieee; use ieee.std_logic_1164.all; use ieee.math_real.all; use ieee.numeric_std.all; use work.RandomPkg.all; use work.CoveragePkg.all; architecture tb3 of tstb is component sxema port (a, b : in std_logic_vector (4 downto 1); d : out std_logic_vector (8 downto 1)); end component; signal a, b : std_logic_vector (4 downto 1); signal d : std_logic_vector (8 downto 1); -- shared variable RndA, RndB : RandomPType; shared variable CovA, CovB, CovD : CovPType ; begin p0 : sxema port map ( a => a, b => b, d => d); RandomGenProc1 : process -- variable RndVal1, RndVal_2 : real; -- Random value variable DataA, DataB,tmp : integer; variable SeedA1 : positive := 7; -- initialize seeds variable SeedA2 : positive := 1; variable SeedB1 : positive := 4; -- initialize seeds variable SeedB2 : positive := 2; variable i : natural := 0; begin -- инициализация генератора псевдослучайных чисел -- RndA.InitSeed(IV => (SeedA1,SeedA2)); -- RndB.InitSeed(IV => (SeedB1,SeedB2)); -- CovA.InitSeed(IV => (SeedA1,SeedA2)); -- CovB.InitSeed(IV => (SeedB1,SeedB2)); CovA.InitSeed(CovA'instance_name); CovB.InitSeed(CovB'instance_name); -- RndA.SetRandomParm ( -- Distribution => NORMAL, -- Mean => 5.0, -- Deviation => 2.0 ) ; -- RndB.SetRandomParm ( -- Distribution => NORMAL, -- Mean => 10.0, -- Deviation => 2.0 ) ; -- создание корзин для a, b, d CovA.AddBins(GenBin(0,15)); CovB.AddBins(GenBin(0,15)); CovD.AddBins(GenBin(0,225)); MainCovLoop: while not (CovA.IsCovered and CovB.IsCovered) loop -- MainCovLoop: while not (CovD.IsCovered) loop -- a <= RndA.RandSlv(0,15,4); -- b <= RndB.RandSlv(0,15,4); (DataA,tmp) := CovA.RandCovPoint ; (DataB,tmp) := CovB.RandCovPoint ; a <= std_logic_vector(to_unsigned(DataA, 4)); b <= std_logic_vector(to_unsigned(DataB, 4)); wait for 10 ns; CovA.ICover(to_integer(unsigned(a))); CovB.ICover(to_integer(unsigned(b))); CovD.ICover(to_integer(unsigned(d))); i := i+1; if i=1000000 then exit; end if; end loop; wait for 10 ns; CovA.WriteBin; CovB.WriteBin; CovD.WriteBin; -- CovA.DumpBin; -- CovA.WriteOrderCount; CovA.WriteCovDb ("CovA.db", OpenKind => WRITE_MODE ); CovB.WriteCovDb ("CovB.db", OpenKind => WRITE_MODE ); CovD.WriteCovDb ("CovD.db", OpenKind => WRITE_MODE ); wait ; end process; end architecture tb3; |

Листинг файла tstb_tb4a

Случайным образом генерит входные A и B с помощью пакета RandomPkg тестбенч для перебора всех пар, проверка перекрёстного покрытия Для покрытия всех пар состояний требуется 2258 циклов покрытие A достигается за 103 циклов покрытие B достигается за 68 циклов

Листинг файла tstb_tb4a.vhd

| Файл: tstb_tb4a.vhd |

-- Случайным образом генерит входные A и B с помощью пакета RandomPkg -- тестбенч для перебора всех пар, проверка перекрёстного покрытия -- Для покрытия всех пар состояний требуется 2258 циклов -- покрытие A достигается за 103 циклов -- покрытие B достигается за 68 циклов library ieee; use ieee.std_logic_1164.all; use ieee.math_real.all; use ieee.numeric_std.all; use work.RandomPkg.all; use work.CoveragePkg.all; architecture tb4a of tstb is component sxema port (a, b : in std_logic_vector (4 downto 1); d : out std_logic_vector (8 downto 1)); end component; signal a, b : std_logic_vector (4 downto 1); signal d : std_logic_vector (8 downto 1); shared variable RndA, RndB : RandomPType; shared variable CovA, CovB, CovD : CovPType ; shared variable CovCrossAB : CovPType ; begin p0 : sxema port map ( a => a, b => b, d => d); RandomGenProc1 : process -- variable RndVal1, RndVal_2 : real; -- Random value variable DataA, DataB,tmp : integer; variable SeedA1 : positive := 7; -- initialize seeds variable SeedA2 : positive := 1; variable SeedB1 : positive := 4; -- initialize seeds variable SeedB2 : positive := 2; variable i : natural := 0; variable CovACovered,CovBCovered : natural := 0; begin -- инициализация генератора псевдослучайных чисел RndA.InitSeed(IV => (SeedA1,SeedA2)); RndB.InitSeed(IV => (SeedB1,SeedB2)); -- CovA.InitSeed(IV => (SeedA1,SeedA2)); -- CovB.InitSeed(IV => (SeedB1,SeedB2)); -- CovA.InitSeed(CovA'instance_name); -- CovB.InitSeed(CovB'instance_name); -- CovCrossAB.InitSeed(CovCrossAB'instance_name); -- RndA.SetRandomParm ( -- Distribution => NORMAL, -- Mean => 5.0, -- Deviation => 2.0 ) ; -- RndB.SetRandomParm ( -- Distribution => NORMAL, -- Mean => 10.0, -- Deviation => 2.0 ) ; -- создание корзин для a, b, d CovA.AddBins(GenBin(0,15)); CovB.AddBins(GenBin(0,15)); CovD.AddBins(GenBin(0,225)); CovCrossAB.AddCross( 2, GenBin(0,15), GenBin(0,15) ); -- MainCovLoop: while not (CovA.IsCovered and CovB.IsCovered) loop MainCovLoop: while not (CovCrossAB.IsCovered) loop a <= RndA.RandSlv(0,15,4); b <= RndB.RandSlv(0,15,4); -- (DataA,DataB) := CovCrossAB.RandCovPoint ; -- a <= std_logic_vector(to_unsigned(DataA, 4)); -- b <= std_logic_vector(to_unsigned(DataB, 4)); wait for 10 ns; CovA.ICover(to_integer(unsigned(a))); CovB.ICover(to_integer(unsigned(b))); CovCrossAB.ICover( (to_integer(unsigned(a)) , to_integer(unsigned(b))) ); CovD.ICover(to_integer(unsigned(d))); i := i+1; if i=1000000 then exit; end if; if (CovA.IsCovered and CovACovered=0) then CovACovered := i; end if; if (CovB.IsCovered and CovBCovered=0) then CovBCovered := i; end if; end loop; wait for 10 ns; CovA.WriteBin; CovB.WriteBin; CovD.WriteBin; CovCrossAB.WriteBin; -- CovA.DumpBin; -- CovA.WriteOrderCount; CovA.WriteCovDb ("CovA.db", OpenKind => WRITE_MODE ); CovB.WriteCovDb ("CovB.db", OpenKind => WRITE_MODE ); CovD.WriteCovDb ("CovD.db", OpenKind => WRITE_MODE ); CovCrossAB.WriteCovDb ("CovCrossAB.db", OpenKind => WRITE_MODE ); wait ; end process; end architecture tb4a; |

Листинг файла tstb_tb4

Случайным образом генерит входные A и B с помощью пакета покрытия, используя перекрёстное покрытие т.е. интеллектуальный тестбенч для перебора всех пар Для покрытия всех пар состояний требуется 512 циклов покрытие A достигается за 49 циклов покрытие B достикается за 44 циклов

Листинг файла tstb_tb4.vhd

| Файл: tstb_tb4.vhd |

-- Случайным образом генерит входные A и B с помощью пакета покрытия, используя перекрёстное покрытие -- т.е. интеллектуальный тестбенч для перебора всех пар -- Для покрытия всех пар состояний требуется 512 циклов -- покрытие A достигается за 49 циклов -- покрытие B достикается за 44 циклов library ieee; use ieee.std_logic_1164.all; use ieee.math_real.all; use ieee.numeric_std.all; use work.RandomPkg.all; use work.CoveragePkg.all; architecture tb4 of tstb is component sxema port (a, b : in std_logic_vector (4 downto 1); d : out std_logic_vector (8 downto 1)); end component; signal a, b : std_logic_vector (4 downto 1); signal d : std_logic_vector (8 downto 1); -- shared variable RndA, RndB : RandomPType; shared variable CovA, CovB, CovD : CovPType ; shared variable CovCrossAB : CovPType ; begin p0 : sxema port map ( a => a, b => b, d => d); RandomGenProc1 : process -- variable RndVal1, RndVal_2 : real; -- Random value variable DataA, DataB,tmp : integer; variable SeedA1 : positive := 7; -- initialize seeds variable SeedA2 : positive := 1; variable SeedB1 : positive := 4; -- initialize seeds variable SeedB2 : positive := 2; variable i : natural := 0; variable CovACovered,CovBCovered : natural := 0; begin -- инициализация генератора псевдослучайных чисел -- RndA.InitSeed(IV => (SeedA1,SeedA2)); -- RndB.InitSeed(IV => (SeedB1,SeedB2)); -- CovA.InitSeed(IV => (SeedA1,SeedA2)); -- CovB.InitSeed(IV => (SeedB1,SeedB2)); CovA.InitSeed(CovA'instance_name); CovB.InitSeed(CovB'instance_name); CovCrossAB.InitSeed(CovCrossAB'instance_name); -- RndA.SetRandomParm ( -- Distribution => NORMAL, -- Mean => 5.0, -- Deviation => 2.0 ) ; -- RndB.SetRandomParm ( -- Distribution => NORMAL, -- Mean => 10.0, -- Deviation => 2.0 ) ; -- создание корзин для a, b, d CovA.AddBins(GenBin(0,15)); CovB.AddBins(GenBin(0,15)); CovD.AddBins(GenBin(0,225)); CovCrossAB.AddCross( 2, GenBin(0,15), GenBin(0,15) ); -- MainCovLoop: while not (CovA.IsCovered and CovB.IsCovered) loop MainCovLoop: while not (CovCrossAB.IsCovered) loop -- a <= RndA.RandSlv(0,15,4); -- b <= RndB.RandSlv(0,15,4); (DataA,DataB) := CovCrossAB.RandCovPoint ; a <= std_logic_vector(to_unsigned(DataA, 4)); b <= std_logic_vector(to_unsigned(DataB, 4)); wait for 10 ns; CovA.ICover(to_integer(unsigned(a))); CovB.ICover(to_integer(unsigned(b))); CovCrossAB.ICover( (to_integer(unsigned(a)) , to_integer(unsigned(b))) ); CovD.ICover(to_integer(unsigned(d))); i := i+1; if i=1000000 then exit; end if; if (CovA.IsCovered and CovACovered=0) then CovACovered := i; end if; if (CovB.IsCovered and CovBCovered=0) then CovBCovered := i; end if; end loop; wait for 10 ns; CovA.WriteBin; CovB.WriteBin; CovD.WriteBin; CovCrossAB.WriteBin; -- CovA.DumpBin; -- CovA.WriteOrderCount; CovA.WriteCovDb ("CovA.db", OpenKind => WRITE_MODE ); CovB.WriteCovDb ("CovB.db", OpenKind => WRITE_MODE ); CovD.WriteCovDb ("CovD.db", OpenKind => WRITE_MODE ); CovCrossAB.WriteCovDb ("CovCrossAB.db", OpenKind => WRITE_MODE ); wait ; end process; end architecture tb4; |

Листинг файла tstb

Листинг файла tstb.vhd

| Файл: tstb.vhd |

|

|