ПЦУСБ/Лекция 4 — различия между версиями

Материал из Wiki

< ПЦУСБ

ANA (обсуждение | вклад) м (→Слайд: Словесное описание автомата) |

ANA (обсуждение | вклад) м (→Слайд: VHDL-модель) |

||

| Строка 136: | Строка 136: | ||

|} | |} | ||

| − | == Слайд: VHDL-модель == | + | == Слайд: VHDL-модель автомата == |

<source lang="vhdl"> | <source lang="vhdl"> | ||

| Строка 188: | Строка 188: | ||

"11" when state="1000" else | "11" when state="1000" else | ||

"00"; | "00"; | ||

| + | end beh; | ||

| + | </source> | ||

| + | |||

| + | |||

| + | == Слайд: VHDL-модель тестбенча == | ||

| + | |||

| + | <source lang="vhdl"> | ||

| + | library ieee; | ||

| + | use ieee.std_logic_1164.all; | ||

| + | |||

| + | entity tb is | ||

| + | |||

| + | end tb; | ||

| + | |||

| + | architecture beh of tb is | ||

| + | |||

| + | component automat | ||

| + | port ( | ||

| + | x : in std_logic_vector(2 downto 1); | ||

| + | rst : in std_logic; | ||

| + | clk : in std_logic; | ||

| + | y : out std_logic_vector(1 downto 0)); | ||

| + | end component; | ||

| + | signal x : std_logic_vector(2 downto 1); | ||

| + | signal rst : std_logic; | ||

| + | signal clk : std_logic := '0'; | ||

| + | signal y : std_logic_vector(1 downto 0); | ||

| + | |||

| + | begin -- beh | ||

| + | |||

| + | automat_1: automat | ||

| + | port map ( | ||

| + | x => x, | ||

| + | rst => rst, | ||

| + | clk => clk, | ||

| + | y => y); | ||

| + | |||

| + | clk <= not clk after 10 ns; | ||

| + | rst <= '1', '0' after 30 ns, | ||

| + | '1' after 400 ns, '0' after 405 ns; | ||

| + | |||

| + | process | ||

| + | begin -- process | ||

| + | |||

| + | x <= "00"; | ||

| + | wait for 55 ns; | ||

| + | x <= "01"; | ||

| + | wait for 20 ns; | ||

| + | x <= "01"; | ||

| + | wait for 20 ns; | ||

| + | x <= "01"; | ||

| + | wait for 20 ns; | ||

| + | x <= "01"; | ||

| + | wait for 40 ns; | ||

| + | x <= "10"; | ||

| + | wait for 40 ns; | ||

| + | x <= "11"; | ||

| + | wait for 40 ns; | ||

| + | x <= "10"; | ||

| + | wait for 40 ns; | ||

| + | x <= "01"; | ||

| + | wait; | ||

| + | end process; | ||

| + | |||

end beh; | end beh; | ||

</source> | </source> | ||

Версия 13:25, 15 октября 2013

- Заголовок

- Цифровые автоматы

- Автор

- Авдеев Н.А.

- Нижний колонтитул

- ПЦУСБ/Лекция 4

- Дополнительный нижний колонтитул

- Авдеев Н.А., 18:44, 25 марта 2014

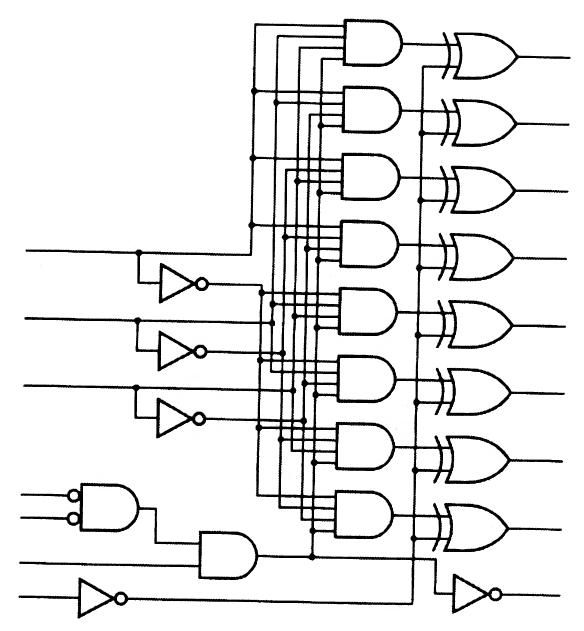

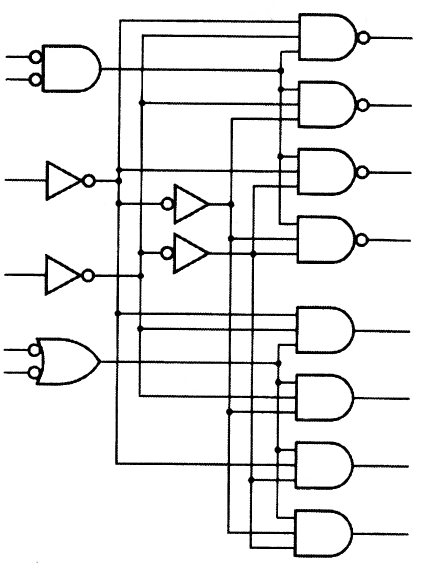

Слайд: Провести анализ схемы (1)

Слайд: Провести анализ схемы (2)

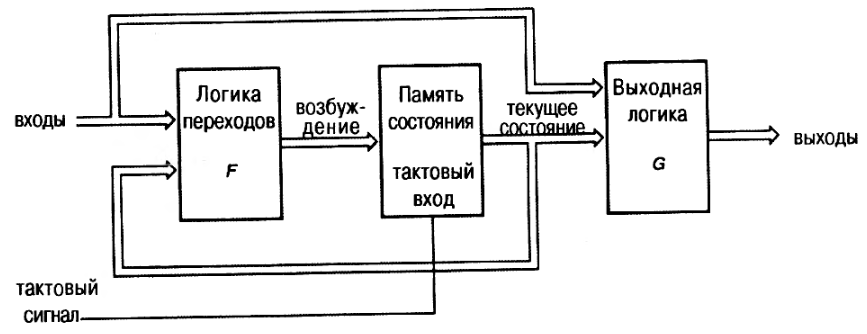

Слайд: Автомат Мили

- Следующее состояние = F (текущее состояние, вход)

- Выход = G (текущее состояние, вход)

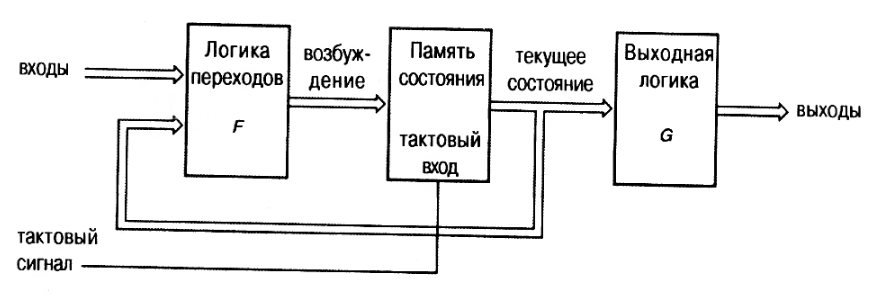

Слайд: Автомат Мура

- Следующее состояние = F (текущее состояние, вход)

- Выход = G (текущее состояние)

Слайд: Граф состояний и переходов

|

|

|

Слайд: Выбор состояний для выходов и кодирование состояний

Слайд: Таблица переходов

| Текущее состояние state |

Входы | Следующее состояние next_state |

|---|---|---|

| "0001" (Q1) | x(1)='1' | "0010" (Q2) |

| "0001" (Q1) | x(1)='0' | "0001" (Q1) |

| "0010" (Q2) | x(2) = '1', x(1)='0' | "0100" (Q3) |

| "0010" (Q2) | x(1)='1' | "1000" (Q4) |

| "0010" (Q2) | x(1)='0' | "0010" (Q2) |

| "1000" (Q4) | x(1)='1' | "0001" (Q1) |

| "1000" (Q4) | x(1)='0' | "1000" (Q4) |

| "0100" (Q3) | - | "0100" (Q3) |

Слайд: Таблица истинности выходной логики

| Состояние State[3:0] |

Выход y[1:0] |

|---|---|

| Q1: "0001" | y1: "00" |

| Q2: "0010" | y2: "10" |

| Q3: "0100" | y1: "00" |

| Q4: "1000" | y3: "11" |

Слайд: VHDL-модель автомата

library ieee; use ieee.std_logic_1164.all; entity automat is port ( x : in std_logic_vector(2 downto 1); rst : in std_logic; clk : in std_logic; y : out std_logic_vector(1 downto 0)); end automat; architecture beh of automat is signal state : std_logic_vector(3 downto 0); signal next_state : std_logic_vector(3 downto 0); begin -- beh -- Задание логики переходов (F) next_state <= "0010" when state="0001" and x(1)='1' else "0001" when state="0001" else "0100" when state="0010" and x(2 downto 1) = "10" else "1000" when state="0010" and x(1)='1' else "0010" when state="0010" else "0001" when state="1000" and x(1)='1' else "1000" when state="1000" else "0100" when state="0100" else "0000"; -- регистр, хранящий текущее состояние p1: process (clk, rst) begin -- process p1 if rst = '1' then state <= "0001"; elsif clk'event and clk = '1' then state <= next_state; end if; end process p1; -- Задание выходной логики (G) y <= "00" when state="0001" else "10" when state="0010" else "00" when state="0100" else "11" when state="1000" else "00"; end beh;

Слайд: VHDL-модель тестбенча

library ieee; use ieee.std_logic_1164.all; entity tb is end tb; architecture beh of tb is component automat port ( x : in std_logic_vector(2 downto 1); rst : in std_logic; clk : in std_logic; y : out std_logic_vector(1 downto 0)); end component; signal x : std_logic_vector(2 downto 1); signal rst : std_logic; signal clk : std_logic := '0'; signal y : std_logic_vector(1 downto 0); begin -- beh automat_1: automat port map ( x => x, rst => rst, clk => clk, y => y); clk <= not clk after 10 ns; rst <= '1', '0' after 30 ns, '1' after 400 ns, '0' after 405 ns; process begin -- process x <= "00"; wait for 55 ns; x <= "01"; wait for 20 ns; x <= "01"; wait for 20 ns; x <= "01"; wait for 20 ns; x <= "01"; wait for 40 ns; x <= "10"; wait for 40 ns; x <= "11"; wait for 40 ns; x <= "10"; wait for 40 ns; x <= "01"; wait; end process; end beh;

Слайд: Словесное описание автомата

Панель ввода пароля

- обеспечить возможность задания нового пароля по нажатию специальной кнопки и ввода старого пароля (пароль по умолчанию 000), а затем ввода нового. При неправильном вводе переходит в начальное состояние (ожидание ввода). При правильном старом пароле включить сигнал "доступ открыт", а после ввода нового пароля отключить сигнал "доступ открыт".

- ввод пароля с клавиатуры (3х значное десятичное число от 000 до 999). Предусмотреть кнопку сброса введённого пароля (при неправильный вводе).

- после ввода 3 цифр система проверяет введённый пароль с внутренним значением:

- если пароли совпадают, то включается светодиод "Доступ открыт" на 3 сек., после чего система переходит в режим ввода пароля

- если пароли не совпадают, то включается звуковой сигнал "Доступ закрыт" на 0.5 сек., после чего система переходит в режим ввода пароля

- если после ввода 1й или 2й цифры, следующая цифра (т.е. 2-я или 3я соответственно) не введены более чем через 5 секунд, то включается звуковой сигнал "Доступ закрыт" на 0.5 секунды

Слайд: Алгоритм

Слайд: Таблица переходов :step

Элементы системы и управляющие сигналы (входы/выходы)

- Входы

- кнопка ввода пароля - сигнал SetPassword

- цифровые кнопки 0-9 - сигналы DigitalKey[8 downto 0]

- кнопка отмены ввода - сигнал Esc

- сигналы (со счетчика) отсчитывающие 0.5, 3, 5 с - Dalay05s, Dalay3s, Dalay5s

- сигнал синхронизации - clk (активный положительный фронт)

- асинхронный сброс - RST

- Выходы

- управление трехразрядным семисегментным индикатором - Digits2[6:0], Digits1[6:0], Digits0[6:0] (реально Digits[6:0] и Index[2:0])

- светодиод "Доступ открыт" - сигнал Open

- Динамик - сигнал Speaker

- Сигнал запуск отсчета паузы - StartCount

Слайд: Таблица переходов

| Текущее состояние | Событие (входы) | Следующее состояние |

|---|---|---|

| Любое | RST = 1 | Начальное состояние (ожидание ввода) |

| Начальное состояние | Нажата кнопка ввода пароля | Режим смены пароля: ввод старого пароля |

| Начальное состояние | Нажата цифровая кнопка | Режим ввода пароля (для доступа) (1) |

| Начальное состояние | Нажата кнопка Esc | Начальное состояние |

| Режим смены пароля: ввод старого пароля (0) | Ввод первой цифры | Режим смены пароля: ввод старого пароля (1), отобразить введённую цифру |

| Режим смены пароля: ввод старого пароля (0) | Прошло 5 с | Начальное состояние |

| Режим смены пароля: ввод старого пароля (1) | Ввод второй цифры | Режим смены пароля: ввод старого пароля (2), отобразить введённую цифру |

| Режим смены пароля: ввод старого пароля (1) | Прошло 5 с | Начальное состояние |

| Режим смены пароля: ввод старого пароля (2) | Ввод третьей цифры | Режим смены пароля:

|

| Режим смены пароля: ввод старого пароля (0-2) | Нажата кнопка Esc | Начальное состояние |

Слайд: Таблица переходов (2)

| Текущее состояние | Событие (входы) | Следующее состояние |

|---|---|---|

| Режим ввода пароля (для доступа) (1) | Ввод второй цифры | Режим ввода пароля (для доступа) (2) |

| Режим ввода пароля (для доступа) (2) | Ввод третьей цифры | Переход в состояние:

|

| Режим ввода пароля (для доступа) (1 или 2) | Прошло 5 с | Начальное состояние |

| доступ открыт | Прошло 3 с | Начальное состояние |

| Доступ закрыт | Прошло 0.5 с | Начальное состояние |

Слайд: Тоже самое в виде графа