ПЦУСБ/Лекция 7 — различия между версиями

Материал из Wiki

< ПЦУСБ

ANA (обсуждение | вклад) (Новая страница: «{{ПЦУСБ TOC}}») |

ANA (обсуждение | вклад) |

||

| Строка 1: | Строка 1: | ||

{{ПЦУСБ TOC}} | {{ПЦУСБ TOC}} | ||

| + | |||

| + | == Классификация ПЛИС == | ||

| + | |||

| + | {| | ||

| + | ![[Файл:1.gif|center]] | ||

| + | |- | ||

| + | ! Классификация программируемых логических интегральных схем (ПЛИС) | ||

| + | |} | ||

| + | |||

| + | * постоянные запоминающие устройства (ПЗУ) | ||

| + | * программируемые логические матрицы (ПЛМ) = Programmable Logic Arrays (PLA) | ||

| + | * программируемые матрицы логики ПМЛ или PAL — Programmable Array Logic (англ.) | ||

| + | * сложные программируемые логические устройства (CPLD = Complex Programmable Logic Device)) | ||

| + | * программируемые пользователем вентильные матрицы (FPGA — Field- Programmable Gate Array) | ||

| + | |||

| + | == Программируемая логическая матрица (ПЛМ) == | ||

| + | |||

| + | |||

| + | {| | ||

| + | ! [[Файл:Обобщенная структура ПЛМ.gif|center|600px]] | ||

| + | |- | ||

| + | ! Обобщенная структура ПЛМ | ||

| + | |} | ||

| + | |||

| + | |||

| + | {| | ||

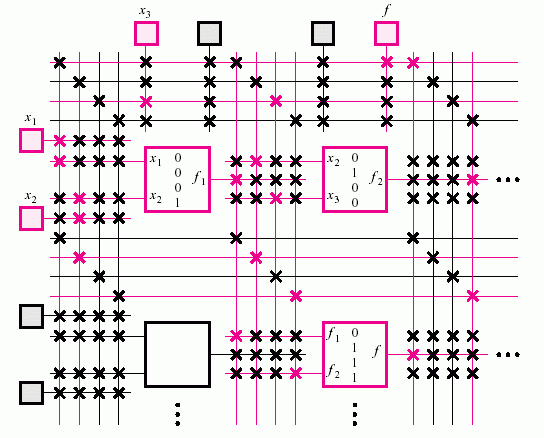

| + | ! [[Файл:Представление внутренней структуры схем ПЛМ.gif|center|600px]] | ||

| + | |- | ||

| + | ! Представление внутренней структуры схем ПЛМ | ||

| + | |||

| + | <m>f_1 = x_1 x_2 + x_1 \overline{x_3} + \overline{x_1} \overline{x_2} x_3</m> | ||

| + | |||

| + | <m>f_2 = x_1 x_2 + \overline{x_1} \overline{x_2} x_3 + x_1 x_3</m> | ||

| + | |||

| + | |} | ||

| + | |||

| + | |||

| + | == Программируемые матрицы логики ПМЛ или PAL == | ||

| + | |||

| + | {| | ||

| + | ! [[Файл:Обобщенная структура ПМЛ.gif|center|600px]] | ||

| + | |- | ||

| + | ! Обобщенная структура ПМЛ | ||

| + | |- | ||

| + | ! <m>f_1 = x_1 x_2 + x_1 \overline{x_3}</m> | ||

| + | |- | ||

| + | ! <m>f_2 = \overline{x_1} \overline{x_2} x_3 + x_1 x_3</m> | ||

| + | |} | ||

| + | |||

| + | == CPLD == | ||

| + | |||

| + | {| | ||

| + | ! [[Файл:Пример внутренней схемы CPLD.gif|center|600px]] | ||

| + | |- | ||

| + | ! Пример внутренней схемы CPLD | ||

| + | |} | ||

| + | |||

| + | |||

| + | {| | ||

| + | ! [[Файл:Внутренняя схема макроячейки микросхемы CPLD.gif|center|600px]] | ||

| + | |- | ||

| + | ! Внутренняя схема макроячейки микросхемы CPLD | ||

| + | |} | ||

| + | |||

| + | |||

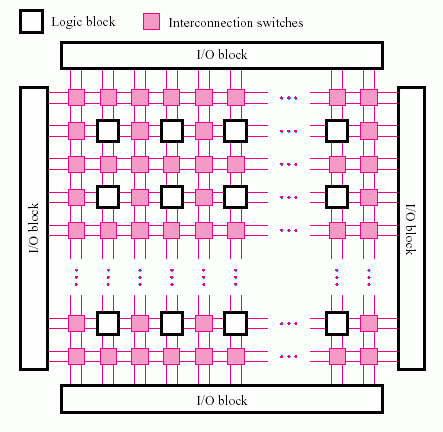

| + | == FPGA == | ||

| + | |||

| + | {| | ||

| + | ! [[Файл:Обобщенная структура микросхем FPGA.png|center|600px]] | ||

| + | |- | ||

| + | ! Обобщенная структура микросхем FPGA | ||

| + | |} | ||

| + | |||

| + | {| | ||

| + | ! [[Файл:Пример внутреннего устройства LUT ПЗУ.gif|center|600px]] | ||

| + | |- | ||

| + | ! Пример внутреннего устройства LUT ПЗУ | ||

| + | |} | ||

| + | |||

| + | {| | ||

| + | ! [[Файл:Пример схемы логического блока FPGA микросхемы.gif|center|600px]] | ||

| + | |- | ||

| + | ! Пример схемы логического блока FPGA микросхемы | ||

| + | |} | ||

| + | |||

| + | {| | ||

| + | ! [[Файл:Пример запрограммированного участка FPGA.png|center|600px]] | ||

| + | |- | ||

| + | ! Пример запрограммированного участка FPGA | ||

| + | |} | ||

| + | |||

| + | * Первые два блока LUT запрограммированы на реализацию функций f1=x1x2 и f2=x2x3. Третий LUT реализует функцию f=f1+f2. | ||

| + | |||

| + | === Структура блока SliceL === | ||

| + | |||

| + | {| | ||

| + | ! [[Файл:Ris SliceL.png|center|600px]] | ||

| + | |- | ||

| + | ! Структура блока SliceL | ||

| + | |} | ||

Версия 00:51, 23 ноября 2013

Содержание |

Классификация ПЛИС

| Классификация программируемых логических интегральных схем (ПЛИС) |

|---|

- постоянные запоминающие устройства (ПЗУ)

- программируемые логические матрицы (ПЛМ) = Programmable Logic Arrays (PLA)

- программируемые матрицы логики ПМЛ или PAL — Programmable Array Logic (англ.)

- сложные программируемые логические устройства (CPLD = Complex Programmable Logic Device))

- программируемые пользователем вентильные матрицы (FPGA — Field- Programmable Gate Array)

Программируемая логическая матрица (ПЛМ)

| Обобщенная структура ПЛМ |

|---|

| Представление внутренней структуры схем ПЛМ

|

|---|

Программируемые матрицы логики ПМЛ или PAL

| Обобщенная структура ПМЛ |

|---|

CPLD

| Пример внутренней схемы CPLD |

|---|

| Внутренняя схема макроячейки микросхемы CPLD |

|---|

FPGA

| Обобщенная структура микросхем FPGA |

|---|

| Пример внутреннего устройства LUT ПЗУ |

|---|

| Пример схемы логического блока FPGA микросхемы |

|---|

| Пример запрограммированного участка FPGA |

|---|

- Первые два блока LUT запрограммированы на реализацию функций f1=x1x2 и f2=x2x3. Третий LUT реализует функцию f=f1+f2.

Структура блока SliceL

| Структура блока SliceL |

|---|