ПЦУСБ/Лабораторная работа 2 — различия между версиями

ANA (обсуждение | вклад) м (→Шпаргалка) |

ANA (обсуждение | вклад) м (→Шпаргалка) |

||

| (не показаны 15 промежуточных версий 1 участника) | |||

| Строка 29: | Строка 29: | ||

=== Требования к оформлению отчета === | === Требования к оформлению отчета === | ||

| − | # В отчете должна быть приведена логическая схема, на которой должны быть обозначены имена сигналов и меток элементов, соответствующие описанию на языке VHDL. | + | # В отчете должна быть приведена логическая схема, на которой должны быть обозначены имена сигналов и меток элементов ({{Зел|как показано на рисунке 2}}), соответствующие структурному описанию на языке VHDL (изображение схемы можно скопировать из файла [[Медиа:ПЦУСБ-ЛР02-tasks.zip|заданий]]). |

| − | # В отчете должен | + | # В отчете должен быть приведён список (таблица) используемых библиотечных элементов, с описанием логических функций и задержек. |

| − | + | # В отчете необходимо привести VHDL-коды: | |

| − | #* | + | #* структурного описания схемы (включая описания используемых библиотечных элементов{{Зел|, которые разместить в приложении А в конце отчета}}) |

| − | #* | + | #* логического описания схемы |

| + | #* тестирующей программы {{Зел|(достаточно одного варианта тестбенча)}}. | ||

# В отчете должны содержаться временные диаграммы, соответствующие тестирующей программе. | # В отчете должны содержаться временные диаграммы, соответствующие тестирующей программе. | ||

| − | # В отчете должна содержаться система логических функций, реализуемых схемой. | + | #* на временной диаграмме должны быть приведены |

| − | # В отчете необходимо привести таблицу, содержащую значения задержки распространения сигналов от входа к выходам для каждого входного набора. | + | #** входы, выходы блоков структурного и логического описаний схемы |

| − | # | + | #** внутренние сигналы структурного и логического описаний схемы |

| − | # В отчете должно быть указано значение задержки схемы, соответствующее задержке критического пути. | + | #** сигнал сравнения выходов |

| + | #** При использовании второго тестбенча, сигналы определения задержек | ||

| + | #* На временных диаграммах должны быть видны все возможные значения входов и соответствующие им значения выходов (например, если 5 входов, то 32 возможных значений входов должны быть различимы на диаграмме). | ||

| + | # В отчете должна содержаться система логических функций, реализуемых схемой ({{Зел|не обязательно, если она совпадает с логическим VHDL-описанием схемы}}). | ||

| + | # В отчете необходимо привести таблицу, содержащую значения задержки распространения сигналов от входа к выходам для каждого входного набора каждой функции. {{Сн|А также, если используется тесбенч считающий задержки, то привести скриншот отчета по задержкам, выдаваемого в транскрипт при выполнении тестбенча.}} | ||

| + | # {{Зел|В отчете необходимо привести схему, на которой должен быть отмечен критический путь для каждой выходной функции}} (как показано на рисунке 3). При этом на схеме для каждого элемента должны быть отмечены (на рисунке розовым цветом): | ||

| + | #* собственная задержка распространения (внутри элемента) | ||

| + | #* и суммарная максимальная задержка распространения сигнала на выходе элемента относительно входов X (на выходе элемента, например, "=7"). | ||

| + | # В отчете должно быть указано значение задержки схемы, соответствующее задержке критического пути. | ||

| + | # {{Зел|В заключении необходимо сравнить значения максимальных задержек для каждого выхода, полученные путём моделирования и ручного анализа. Если значения не совпадают, то выявить причину и привести пояснения этому (провести анализ причин несовпадения).}} | ||

| + | |||

| + | Требования к VHDL-файлам проекта: | ||

| + | * Описания всех элементов должны быть в отдельных файлах, <s>при этом каждый файл должен включать следующий комментарий: | ||

| + | ** ФИО и номер группы автора разработанной VHDL-модели; | ||

| + | ** номер варианта;</s> | ||

| + | |||

| + | |||

| + | {{Info|Если в комментариях используете русский алфавит, то кодировку текстового файла нужно выбирать UTF-8. В стандартной Windows кодировке (cp1251) могут наблюдаться фиктивные ошибки при компиляции VHDL кода. Для задания кодировки в ModelSim нужно выполнить команду <code>encoding system utf-8</code> в терминальном окне (там куда выводятся системные сообщения).}} | ||

=== Библиотека элементов === | === Библиотека элементов === | ||

| Строка 52: | Строка 70: | ||

! Имя элемента | ! Имя элемента | ||

! Функция элемента | ! Функция элемента | ||

| − | ! Задержка, <br /> относит. ед. | + | ! Задержка, <br /> относит. ед.<br /> (гр. 013202) |

! Площадь | ! Площадь | ||

| − | ! Задержка, пс | + | ! Задержка, пс<br /> (гр. 013201) |

|- | |- | ||

| GND | | GND | ||

| Строка 163: | Строка 181: | ||

! [[Файл:Alib3-logic.png|600px]] | ! [[Файл:Alib3-logic.png|600px]] | ||

|- | |- | ||

| − | ! Рисунок | + | ! Рисунок 2 – Условное графическое обозначение элементов |

|} | |} | ||

| Строка 172: | Строка 190: | ||

{{Info|Для группы 013201 вариант задания соответствует номеру в журнале. <br /> Для группы 013202 вариант задания определяется по формуле (31 – N), где N – номер по списку в группе.}} | {{Info|Для группы 013201 вариант задания соответствует номеру в журнале. <br /> Для группы 013202 вариант задания определяется по формуле (31 – N), где N – номер по списку в группе.}} | ||

| + | |||

| + | {{Info|Группа 013201 моделирует задержки с точностью пс, поэтому нужно установить параметр '''Resolution''' при запуске моделирования равным '''ps'''}} | ||

== Шпаргалка == | == Шпаргалка == | ||

| Строка 178: | Строка 198: | ||

! <html><img src="https://docs.google.com/drawings/d/10Tk3WXQRDjZxECs6GPA9UKKyr7WJyYoDxIG4VPl48Mw/pub?w=800"></html> | ! <html><img src="https://docs.google.com/drawings/d/10Tk3WXQRDjZxECs6GPA9UKKyr7WJyYoDxIG4VPl48Mw/pub?w=800"></html> | ||

|- | |- | ||

| − | ! Схема | + | ! Рисунок 3 — Схема |

|} | |} | ||

| Строка 363: | Строка 383: | ||

| − | {{Hider|VHDL-модель пакета lib }} | + | Чтобы уменьшить размер файла структурного описания схемы, декларации элементов (описание интерфейсов) выносятся в пакет <code>lib</code> (package), который будет подключаться в структурной VHDL модели через оператор <code>use work.lib.all;</code> |

| + | |||

| + | |||

| + | {{Hider|VHDL-модель пакета lib (файл lib_p.vhd)}} | ||

{{Файл|lib_p.vhd| | {{Файл|lib_p.vhd| | ||

<source lang="vhdl"> | <source lang="vhdl"> | ||

| Строка 619: | Строка 642: | ||

{{Hider|end}} | {{Hider|end}} | ||

| + | |||

| + | Тестбенч sch01_tb(tb) позволяет проверить правильность работы двух VHDL описаний схемы, но определение задержки по выходам для каждого набора нужно делать вручную, используя два курсора на временных диаграммах как показано на рисунке 4. | ||

| + | |||

| + | |||

| + | {| align=center | ||

| + | ! [[Файл:Lab02-wave-cursors.png|center]] | ||

| + | |- | ||

| + | ! Рисунок 4 — Временная диаграмма тестбенча (sch01_tb(tb)) | ||

| + | |} | ||

| + | |||

| + | |||

| + | Определение задержек можно автоматизировать, для этого необходимо дополнить тесбенч соответствующим описанием. | ||

{{Hider|VHDL-модель тестбенча (sch01_tb2.vhd)}} | {{Hider|VHDL-модель тестбенча (sch01_tb2.vhd)}} | ||

| − | {{Info|Компилировать файл sch01_tb2.vhd нужно с выставленной опцией совместимости со стандартом VHDL-2008. <br /> В противном случае будет выдаваться ошибка об отсутствии функции to_string или write}} | + | <!-- {{Info|Компилировать файл sch01_tb2.vhd нужно с выставленной опцией совместимости со стандартом VHDL-2008. <br /> В противном случае будет выдаваться ошибка об отсутствии функции to_string или write}} --> |

| Строка 632: | Строка 667: | ||

use std.textio.all; | use std.textio.all; | ||

use ieee.std_logic_textio.all; | use ieee.std_logic_textio.all; | ||

| − | + | ||

------------------------------------------------------------------------------- | ------------------------------------------------------------------------------- | ||

| − | + | ||

--entity sch01_tb is | --entity sch01_tb is | ||

--end entity sch01_tb; | --end entity sch01_tb; | ||

| − | + | ||

------------------------------------------------------------------------------- | ------------------------------------------------------------------------------- | ||

| − | + | ||

architecture tb2 of sch01_tb is | architecture tb2 of sch01_tb is | ||

| − | + | -- функция для преобразования вектора (std_logic_vector) в строку символов (string) | |

| + | function to_string (vec : std_logic_vector) return string is | ||

| + | alias v : std_logic_vector(1 to vec'length) is vec; | ||

| + | variable str : string(v'range); | ||

| + | begin -- function to_string | ||

| + | for i in v'range loop | ||

| + | if v(i) = '1' then | ||

| + | str(i) := '1'; | ||

| + | else | ||

| + | str(i) := '0'; | ||

| + | end if; | ||

| + | end loop ; | ||

| + | return str; | ||

| + | end function to_string; | ||

| + | |||

component sch01 is | component sch01 is | ||

port ( | port ( | ||

| Строка 647: | Строка 696: | ||

Y : out std_logic_vector(2 downto 1)); | Y : out std_logic_vector(2 downto 1)); | ||

end component sch01; | end component sch01; | ||

| − | + | ||

component sch01a is | component sch01a is | ||

port ( | port ( | ||

| Строка 653: | Строка 702: | ||

Y : out std_logic_vector(2 downto 1)); | Y : out std_logic_vector(2 downto 1)); | ||

end component sch01a; | end component sch01a; | ||

| − | + | ||

signal X : std_logic_vector(2 downto 0) := (others => '0'); | signal X : std_logic_vector(2 downto 0) := (others => '0'); | ||

signal Y1 : std_logic_vector(2 downto 1); | signal Y1 : std_logic_vector(2 downto 1); | ||

signal Y2 : std_logic_vector(2 downto 1); | signal Y2 : std_logic_vector(2 downto 1); | ||

| − | + | ||

signal OK : std_logic; | signal OK : std_logic; | ||

signal All_Ok : std_logic; | signal All_Ok : std_logic; | ||

signal strob : std_logic := '0'; | signal strob : std_logic := '0'; | ||

| − | + | ||

signal clock_time : time := 0 ns; | signal clock_time : time := 0 ns; | ||

signal delay_y1, delay_y1_max : time := 0 ns; | signal delay_y1, delay_y1_max : time := 0 ns; | ||

signal delay_y2, delay_y2_max : time := 0 ns; | signal delay_y2, delay_y2_max : time := 0 ns; | ||

| − | + | ||

begin | begin | ||

| − | + | ||

DUT1 : sch01 | DUT1 : sch01 | ||

port map ( | port map ( | ||

X => X, | X => X, | ||

Y => Y1); | Y => Y1); | ||

| − | + | ||

DUT2 : sch01a | DUT2 : sch01a | ||

port map ( | port map ( | ||

X => X, | X => X, | ||

Y => Y2); | Y => Y2); | ||

| − | + | ||

-- формирование входных воздействий | -- формирование входных воздействий | ||

x(0) <= not x(0) after 50 ns; | x(0) <= not x(0) after 50 ns; | ||

x(1) <= not x(1) after 100 ns; | x(1) <= not x(1) after 100 ns; | ||

x(2) <= not x(2) after 200 ns; | x(2) <= not x(2) after 200 ns; | ||

| − | + | ||

-- процесс формирует стробирующий сигнал, | -- процесс формирует стробирующий сигнал, | ||

-- по положительному фронту которого происходит сравнение | -- по положительному фронту которого происходит сравнение | ||

| Строка 693: | Строка 742: | ||

wait for 5 ns; | wait for 5 ns; | ||

end process; | end process; | ||

| − | + | ||

-- проверка соответствия ответов | -- проверка соответствия ответов | ||

OK <= | OK <= | ||

'1' when Y1 = Y2 else | '1' when Y1 = Y2 else | ||

'X'; | 'X'; | ||

| − | + | ||

-- определение времени смены входных сигналов | -- определение времени смены входных сигналов | ||

clock_time <= | clock_time <= | ||

now when x(0)'event else | now when x(0)'event else | ||

clock_time; | clock_time; | ||

| − | + | ||

-- определение задержки распространения сигнала от входов к выходам | -- определение задержки распространения сигнала от входов к выходам | ||

delay_y1 <= | delay_y1 <= | ||

| Строка 709: | Строка 758: | ||

0 ns when x(0)'event else | 0 ns when x(0)'event else | ||

delay_y1; | delay_y1; | ||

| − | + | ||

delay_y2 <= | delay_y2 <= | ||

now - clock_time when y1(2)'event else | now - clock_time when y1(2)'event else | ||

0 ns when clock_time'event else | 0 ns when clock_time'event else | ||

delay_y2; | delay_y2; | ||

| − | + | ||

-- определение максимальной задержки распространения сигнала | -- определение максимальной задержки распространения сигнала | ||

delay_y1_max <= | delay_y1_max <= | ||

delay_y1 when delay_y1 >= delay_y1_max else | delay_y1 when delay_y1 >= delay_y1_max else | ||

delay_y1_max; | delay_y1_max; | ||

| − | + | ||

delay_y2_max <= | delay_y2_max <= | ||

| − | 0 ns when now < 100 ns else | + | 0 ns when now < 100 ns else -- отключение определения максимальной задержки на 100 нс (не всем это нужно) |

delay_y2 when delay_y2 >= delay_y2_max else | delay_y2 when delay_y2 >= delay_y2_max else | ||

delay_y2_max; | delay_y2_max; | ||

| − | + | ||

-- процесс для вывода значений задержки в транскрипт | -- процесс для вывода значений задержки в транскрипт | ||

process (strob) | process (strob) | ||

| + | variable t1 : bit_vector(5 downto 0) := "101010"; | ||

begin -- process | begin -- process | ||

if strob'event and strob = '1' then | if strob'event and strob = '1' then | ||

-- write(OUTPUT, " " & time'image(now) & " " & to_string(x) & " " & to_string(y1) & " " & time'image(delay_y2)& " " & time'image(delay_y1) & LF ); | -- write(OUTPUT, " " & time'image(now) & " " & to_string(x) & " " & to_string(y1) & " " & time'image(delay_y2)& " " & time'image(delay_y1) & LF ); | ||

| + | |||

| + | write(OUTPUT, " " & to_string(x) & " " & to_string(y1) & " " & time'image(delay_y2)& " " & time'image(delay_y1) ); | ||

| − | |||

if y1 = y2 then | if y1 = y2 then | ||

All_Ok <= '1'; | All_Ok <= '1'; | ||

| Строка 739: | Строка 790: | ||

write(OUTPUT, " FAIL" & LF); | write(OUTPUT, " FAIL" & LF); | ||

end if; | end if; | ||

| − | + | ||

end if; | end if; | ||

| − | + | ||

end process; | end process; | ||

| − | + | ||

end architecture tb2; | end architecture tb2; | ||

</source> | </source> | ||

| Строка 753: | Строка 804: | ||

! [[Файл:ЦСУСБ-Лаб2-Tb2 vawe.png|800px|center]] | ! [[Файл:ЦСУСБ-Лаб2-Tb2 vawe.png|800px|center]] | ||

|- | |- | ||

| − | ! Временная диаграмма sch01_tb(tb2) | + | ! Рисунок 5 – Временная диаграмма тесбенча (sch01_tb(tb2)) |

|} | |} | ||

| Строка 783: | Строка 834: | ||

* D<sub>Y1</sub> = 10 нс (условных единиц) | * D<sub>Y1</sub> = 10 нс (условных единиц) | ||

* D<sub>Y2</sub> = 7 нс (условных единиц) | * D<sub>Y2</sub> = 7 нс (условных единиц) | ||

| − | Начальное значение задержки (9 нс) "фиктивное". | + | Начальное значение задержки (9 нс) для функции Y2 "фиктивное", поэтому в описании поведения сигнала delay_y2_max добавлена дополнительная строка обнуляющая delay_y2_max начальные 100 нс. |

Однако, при ручном анализе схемы: | Однако, при ручном анализе схемы: | ||

| Строка 790: | Строка 841: | ||

! <html><img src="https://docs.google.com/drawings/d/1XZO6wtpykyefcsPqQfV27MHfzaKG82h0ff1AutnV7fA/pub?w=800"></html> | ! <html><img src="https://docs.google.com/drawings/d/1XZO6wtpykyefcsPqQfV27MHfzaKG82h0ff1AutnV7fA/pub?w=800"></html> | ||

|- | |- | ||

| − | ! Схема с отмеченным критическим путём для каждого выхода ([https://docs.google.com/drawings/d/1XZO6wtpykyefcsPqQfV27MHfzaKG82h0ff1AutnV7fA/edit Edit]) | + | ! Рисунок 6 — Схема с отмеченным критическим путём для каждого выхода ([https://docs.google.com/drawings/d/1XZO6wtpykyefcsPqQfV27MHfzaKG82h0ff1AutnV7fA/edit Edit]) |

|} | |} | ||

Текущая версия на 09:27, 20 декабря 2013

- Лабораторная работа 1

- Лабораторная работа 2

- Лабораторная работа 3

- Лабораторная работа 4

Содержание |

Описание и моделирование нерегулярных логических схем

Задание

| Рисунок 1 — Пример задания схемы |

|---|

Для заданной нерегулярной логической схемы (см. пример на рисунке 1):

- составить структурное VHDL-описание;

- построить систему логических функций, реализуемую схемой и составить VHDL-описание по полученным выражениям;

- составить тестбенч для проверки эквивалентности двух VHDL-описаний, выполнив моделирование на всех наборах значений входных переменных;

- найти критический путь в схеме.

Рекомендуемый порядок выполнения работы

- Составить VHDL-модель каждого из типов элементов, входящих в схему. Если в схеме есть элементы одинакового типа, то составляется одна модель для всех элементов данного типа. Модель элемента должна учитывать задержку распространения сигнала (от входа к выходу), указанную в таблице 1. В схеме для каждого логического элемента указаны его тип (библиотечное имя) и имена входных и выходных портов.

- Составить структурную VHDL-модель схемы в целом. Предварительно следует проставить на схеме имена связей и номера элементов, которые должны соответствовать именам сигналов и меткам элементов (в операторе port map).

- По схеме составить логические уравнения зависимости выходов от входов, используя заданные в таблице 1 логические функции элементов. Составить VHDL-модель, используя полученные выражения.

- Составить тестирующую программу, включающую две VHDL-модели, и формирующую входные сигналы (полный перебор) и сравнивая ответы двух схем (сигнал OK). При сравнении ответов следует учитывать, что в структурном VHDL-описании учитываются задержки распространения сигналов в логических элементах, и поэтому правильные (окончательные) ответы со структурного и логического описаний будут разнесены во времени.

- Провести моделирование и получить временную диаграмму.

- Для каждого тестирующего набора и для каждой функции определить задержку схемы.

- Найти критический путь на схеме – путь с наибольшей суммарной задержкой элементов.

Требования к оформлению отчета

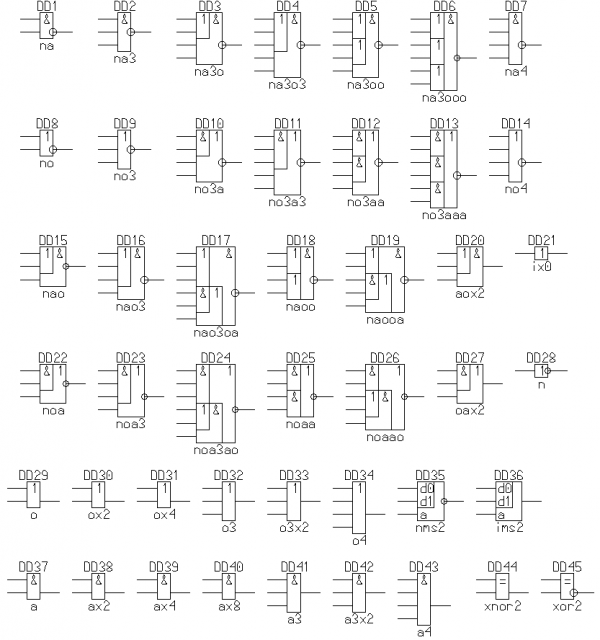

- В отчете должна быть приведена логическая схема, на которой должны быть обозначены имена сигналов и меток элементов (как показано на рисунке 2), соответствующие структурному описанию на языке VHDL (изображение схемы можно скопировать из файла заданий).

- В отчете должен быть приведён список (таблица) используемых библиотечных элементов, с описанием логических функций и задержек.

- В отчете необходимо привести VHDL-коды:

- структурного описания схемы (включая описания используемых библиотечных элементов, которые разместить в приложении А в конце отчета)

- логического описания схемы

- тестирующей программы (достаточно одного варианта тестбенча).

- В отчете должны содержаться временные диаграммы, соответствующие тестирующей программе.

- на временной диаграмме должны быть приведены

- входы, выходы блоков структурного и логического описаний схемы

- внутренние сигналы структурного и логического описаний схемы

- сигнал сравнения выходов

- При использовании второго тестбенча, сигналы определения задержек

- На временных диаграммах должны быть видны все возможные значения входов и соответствующие им значения выходов (например, если 5 входов, то 32 возможных значений входов должны быть различимы на диаграмме).

- на временной диаграмме должны быть приведены

- В отчете должна содержаться система логических функций, реализуемых схемой (не обязательно, если она совпадает с логическим VHDL-описанием схемы).

- В отчете необходимо привести таблицу, содержащую значения задержки распространения сигналов от входа к выходам для каждого входного набора каждой функции. А также, если используется тесбенч считающий задержки, то привести скриншот отчета по задержкам, выдаваемого в транскрипт при выполнении тестбенча.

- В отчете необходимо привести схему, на которой должен быть отмечен критический путь для каждой выходной функции (как показано на рисунке 3). При этом на схеме для каждого элемента должны быть отмечены (на рисунке розовым цветом):

- собственная задержка распространения (внутри элемента)

- и суммарная максимальная задержка распространения сигнала на выходе элемента относительно входов X (на выходе элемента, например, "=7").

- В отчете должно быть указано значение задержки схемы, соответствующее задержке критического пути.

- В заключении необходимо сравнить значения максимальных задержек для каждого выхода, полученные путём моделирования и ручного анализа. Если значения не совпадают, то выявить причину и привести пояснения этому (провести анализ причин несовпадения).

Требования к VHDL-файлам проекта:

- Описания всех элементов должны быть в отдельных файлах,

при этом каждый файл должен включать следующий комментарий:- ФИО и номер группы автора разработанной VHDL-модели;

- номер варианта;

Библиотека элементов

В таблице заданы 2 типа задержек: в относительных единицах и в пикосекундах. Относительные единицы можно приравнять к наносекундам.

| |

Группа 013201 должна использовать значения задержки в пикосекундах, |

| Имя элемента | Функция элемента | Задержка, относит. ед. (гр. 013202) |

Площадь | Задержка, пс (гр. 013201) |

|---|---|---|---|---|

| GND | 1 | — | — | |

| VCC | 1 | — | — | |

| N | 2 | 100 | 160 | |

| A2 | 4 | 1000 | 511 | |

| A3 | 5 | 1500 | 824 | |

| A4 | 6 | 400 | 1156 | |

| A6 | 10 | 400 | 1505 | |

| A8 | 12 | 400 | 2121 | |

| EX2 | 7 | 1000 | 592 | |

| MX2 | 8 | 1000 | 938 | |

| NA2 | 3 | 200 | 275 | |

| NA3 | 4 | 300 | 425 | |

| NA3O2 | 5 | 300 | 441 | |

| NA4 | 5 | 400 | 742 | |

| NAO2 | 4 | 200 | 362 | |

| NAO22 | 5 | 200 | 487 | |

| NAO3 | 5 | 300 | 1000 | |

| NAOA2 | 5 | 200 | 1000 | |

| NEX2 | 7 | 1000 | 526 | |

| NMX2 | 6 | 1000 | 593 | |

| NMX4 | 15 | 1000 | 910 | |

| NO2 | 3 | 200 | 299 | |

| NO3 | 4 | 300 | 559 | |

| NO3A2 | 5 | 300 | 643 | |

| NO4 | 5 | 400 | 1087 | |

| NOA2 | 4 | 200 | 346 | |

| NOA22 | 5 | 200 | 477 | |

| NOA3 | 5 | 300 | 570 | |

| NOAO2 | 5 | 200 | 570 | |

| O2 | 4 | 1000 | 601 | |

| O3 | 5 | 1500 | 946 | |

| O4 | 6 | 1500 | 1400 | |

| O6 | 10 | 1500 | 1831 | |

| O8 | 12 | 1500 | 2388 | |

| DFRS | D-триггер, управляемый положительным фронтом с

асинхронным сбросом и установкой с прямым выходом |

25 | 1000 | 1300 |

|

|---|

| Рисунок 2 – Условное графическое обозначение элементов |

Варианты заданий

Варианты заданий приведены в DOC-файле.

| |

Для группы 013201 вариант задания соответствует номеру в журнале. |

| |

Группа 013201 моделирует задержки с точностью пс, поэтому нужно установить параметр Resolution при запуске моделирования равным ps |

Шпаргалка

| |

|---|

| Рисунок 3 — Схема |

1. На схеме подписываются все связи и даются имена всем элементам. Подписывать элементы рекомендуется как принято в ГОСТе: слева направо, сверху вниз. Рекомендуется использовать префикс DD в метке элемента.

2. Определяется список библиотечных элементов, входящих в схему.

| Имя элемента | Функция элемента | Задержка, относит. ед. |

Площадь | Задержка, пс |

|---|---|---|---|---|

| N | 2 | 100 | 160 | |

| NA3 | 4 | 300 | 425 | |

| NO2 | 3 | 200 | 299 | |

| NAO22 | 5 | 200 | 487 | |

| NOAO2 | 5 | 200 | 570 |

По функциям заданным в таблице составляются соответствующие VHDL описания используемых логических элементов. Для примера будем использовать задержки заданные в условных единицах, которые приравняем к наносекундам (т.е. значения заданные в таблице домножим на 1 нс).

| Файл: N.vhd |

ibrary ieee; use ieee.std_logic_1164.all; entity n is generic ( del : time := 2 ns); port ( A : in std_logic; Y : out std_logic); end entity n; architecture beh of n is begin -- architecture beh Y <= not A after del; end architecture beh; |

| Файл: NO2.vhd |

library ieee; use ieee.std_logic_1164.all; entity NO2 is port ( A, B : in std_logic; Y : out std_logic); end entity NO2; architecture beh of NO2 is begin -- architecture beh Y <= not (A or B) after 3 ns; end architecture beh; |

| Файл: NA3.vhd |

library ieee; use ieee.std_logic_1164.all; entity NA3 is generic ( del : time := 4 ns); port ( A : in std_logic; B : in std_logic; C : in std_logic; Y : out std_logic); end entity NA3; architecture beh of NA3 is begin -- architecture beh Y <= not (A and B and C) after del; end architecture beh; |

| Файл: NAO22.vhd |

library ieee; use ieee.std_logic_1164.all; entity NAO22 is generic ( del : time := 5 ns); port ( A : in std_logic; B : in std_logic; C : in std_logic; D : in std_logic; Y : out std_logic); end entity NAO22; architecture beh of NAO22 is begin Y <= not ((A or B) and (C or D)) after del; end architecture beh; |

| Файл: NOAO2.vhd |

library ieee; use ieee.std_logic_1164.all; entity NOAO2 is generic ( -- del : time := 570 ps); del : time := 5 ns); port ( A : in std_logic; B : in std_logic; C : in std_logic; D : in std_logic; Y : out std_logic); end entity NOAO2; architecture beh of NOAO2 is begin Y <= not (A or (B and (C or D))) after del; end architecture beh; |

Чтобы уменьшить размер файла структурного описания схемы, декларации элементов (описание интерфейсов) выносятся в пакет lib (package), который будет подключаться в структурной VHDL модели через оператор use work.lib.all;

| Файл: lib_p.vhd |

------------------------------------------------------------------------------- -- Project : Lab02 -- Variant : 01 -- Author : ANA (XXX group) ------------------------------------------------------------------------------- library ieee; use ieee.std_logic_1164.all; package lib is component n is generic ( del : time := 2 ns); port ( A : in std_logic; Y : out std_logic); end component n; component NO2 is port ( A, B : in std_logic; Y : out std_logic); end component NO2; component NA3 is -- generic ( -- del : time :); port ( A : in std_logic; B : in std_logic; C : in std_logic; Y : out std_logic); end component NA3; component NAO22 is generic ( del : time := 5 ns); port ( A : in std_logic; B : in std_logic; C : in std_logic; D : in std_logic; Y : out std_logic); end component NAO22; component NOAO2 is generic ( del : time := 5 ns); port ( A : in std_logic; B : in std_logic; C : in std_logic; D : in std_logic; Y : out std_logic); end component NOAO2; end package lib; |

| Файл: sch01.vhd |

------------------------------------------------------------------------------- -- Project : Lab02 -- Variant : 01 -- Author : ANA (XXX group) ------------------------------------------------------------------------------- library ieee; use ieee.std_logic_1164.all; use work.lib.all; entity sch01 is port ( X : in std_logic_vector(3 downto 1); Y : out std_logic_vector(2 downto 1)); end entity sch01; architecture sch of sch01 is signal x1_n, x2_n, x3_n : std_logic; signal DD3_Y : std_logic; signal DD4_Y : std_logic; signal DD5_Y : std_logic; signal DD5_YN : std_logic; signal DD8_Y : std_logic; begin DD1: n port map (X(1), X1_N); DD2: n port map (A => X(2), Y => X2_N); DD3: NO2 port map ( A => X1_N, B => X(2), Y => DD3_Y); DD4: NO2 port map (X(1), X(3), DD4_Y); DD5: NA3 port map ( A => x2_N, B => X(1), C => x(3), Y => DD5_Y); DD6: n port map (DD5_Y, DD5_YN); DD7: n port map (X(3), X3_N); DD8: NA3 port map ( A => x(1), B => DD4_Y, C => x(3), Y => DD8_Y); DD9: NAO22 port map ( A => DD3_Y, B => DD4_Y, C => DD8_Y, D => DD5_YN, Y => Y(1)); DD10: NOAO2 port map ( A => X(1), B => X3_N, C => DD3_Y, D => DD5_Y, Y => Y(2)); end architecture sch; |

| Файл: sch01_log.vhd |

------------------------------------------------------------------------------- -- Project : Lab02 -- Variant : 01 -- Author : ANA (XXX group) ------------------------------------------------------------------------------- library ieee; use ieee.std_logic_1164.all; use work.lib.all; entity sch01a is port ( X : in std_logic_vector(3 downto 1); Y : out std_logic_vector(2 downto 1)); end entity sch01a; architecture log of sch01a is signal DD3_Y : std_logic; signal DD4_Y : std_logic; signal DD5_Y : std_logic; signal DD8_Y : std_logic; begin -- DD3: NO2 DD3_Y <= not ( not X(1) or X(2) ); -- DD4: NO2 DD4_Y <= not ( X(1) or X(3) ); -- DD5: NA3 DD5_Y <= not ( not x(2) and X(1) and x(3) ); -- DD8: NA3 DD8_Y <= not (x(1) and DD4_Y and x(3)); -- DD9: NAO22 Y(1) <= not ((DD3_Y or DD4_Y) and (DD8_Y or not DD5_Y)); -- DD10: NOAO2 Y(2) <= not (X(1) or (not x(3) and (DD3_Y or DD5_Y))); end architecture log; |

| Файл: sch01_tb.vhd |

------------------------------------------------------------------------------- -- Project : Lab02 -- Variant : 01 -- Author : ANA (XXX group) ------------------------------------------------------------------------------- library ieee; use ieee.std_logic_1164.all; entity sch01_tb is end entity sch01_tb; architecture tb of sch01_tb is -- components component sch01 is port ( X : in std_logic_vector(3 downto 1); Y : out std_logic_vector(2 downto 1)); end component sch01; component sch01a is port ( X : in std_logic_vector(3 downto 1); Y : out std_logic_vector(2 downto 1)); end component sch01a; signal X : std_logic_vector(2 downto 0) := (others => '0'); signal Y1 : std_logic_vector(2 downto 1); signal Y2 : std_logic_vector(2 downto 1); signal OK : std_logic; begin DUT1: sch01 port map ( X => X, Y => Y1); DUT2: sch01a port map ( X => X, Y => Y2); x(0) <= not x(0) after 50 ns; x(1) <= not x(1) after 100 ns; x(2) <= not x(2) after 200 ns; OK <= '1' when Y1 = Y2 else 'X'; end architecture tb; |

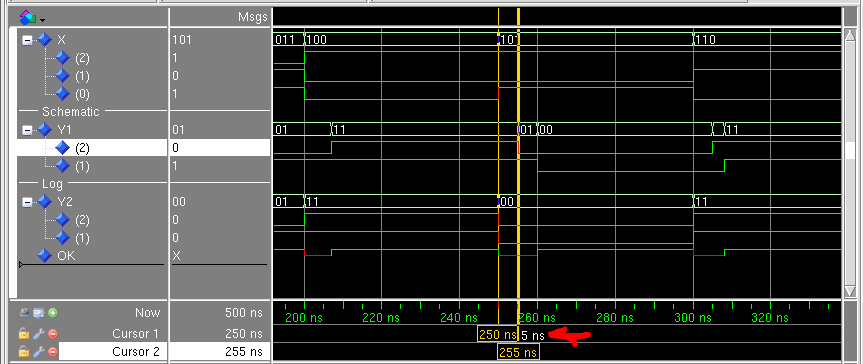

Тестбенч sch01_tb(tb) позволяет проверить правильность работы двух VHDL описаний схемы, но определение задержки по выходам для каждого набора нужно делать вручную, используя два курсора на временных диаграммах как показано на рисунке 4.

| Рисунок 4 — Временная диаграмма тестбенча (sch01_tb(tb)) |

|---|

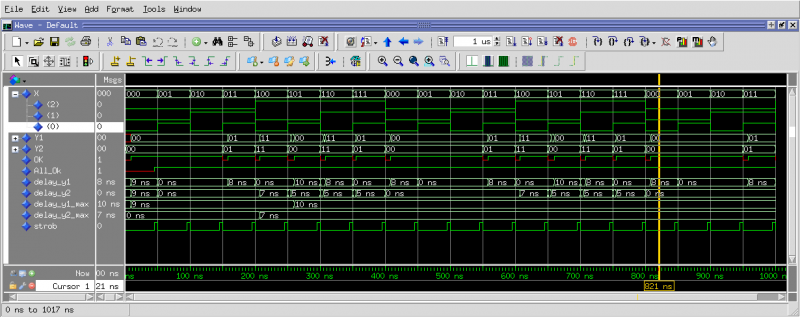

Определение задержек можно автоматизировать, для этого необходимо дополнить тесбенч соответствующим описанием.

| Файл: sch01_tb2.vhd |

library ieee; use ieee.std_logic_1164.all; -- пакеты для ввода/вывода use std.textio.all; use ieee.std_logic_textio.all; ------------------------------------------------------------------------------- --entity sch01_tb is --end entity sch01_tb; ------------------------------------------------------------------------------- architecture tb2 of sch01_tb is -- функция для преобразования вектора (std_logic_vector) в строку символов (string) function to_string (vec : std_logic_vector) return string is alias v : std_logic_vector(1 to vec'length) is vec; variable str : string(v'range); begin -- function to_string for i in v'range loop if v(i) = '1' then str(i) := '1'; else str(i) := '0'; end if; end loop ; return str; end function to_string; component sch01 is port ( X : in std_logic_vector(3 downto 1); Y : out std_logic_vector(2 downto 1)); end component sch01; component sch01a is port ( X : in std_logic_vector(3 downto 1); Y : out std_logic_vector(2 downto 1)); end component sch01a; signal X : std_logic_vector(2 downto 0) := (others => '0'); signal Y1 : std_logic_vector(2 downto 1); signal Y2 : std_logic_vector(2 downto 1); signal OK : std_logic; signal All_Ok : std_logic; signal strob : std_logic := '0'; signal clock_time : time := 0 ns; signal delay_y1, delay_y1_max : time := 0 ns; signal delay_y2, delay_y2_max : time := 0 ns; begin DUT1 : sch01 port map ( X => X, Y => Y1); DUT2 : sch01a port map ( X => X, Y => Y2); -- формирование входных воздействий x(0) <= not x(0) after 50 ns; x(1) <= not x(1) after 100 ns; x(2) <= not x(2) after 200 ns; -- процесс формирует стробирующий сигнал, -- по положительному фронту которого происходит сравнение -- выходов двух моделей и вывод в транскрипт значений задержки process is begin -- process strob <= '0'; wait for 45 ns; strob <= '1'; wait for 5 ns; end process; -- проверка соответствия ответов OK <= '1' when Y1 = Y2 else 'X'; -- определение времени смены входных сигналов clock_time <= now when x(0)'event else clock_time; -- определение задержки распространения сигнала от входов к выходам delay_y1 <= now - clock_time when y1(1)'event else 0 ns when x(0)'event else delay_y1; delay_y2 <= now - clock_time when y1(2)'event else 0 ns when clock_time'event else delay_y2; -- определение максимальной задержки распространения сигнала delay_y1_max <= delay_y1 when delay_y1 >= delay_y1_max else delay_y1_max; delay_y2_max <= 0 ns when now < 100 ns else -- отключение определения максимальной задержки на 100 нс (не всем это нужно) delay_y2 when delay_y2 >= delay_y2_max else delay_y2_max; -- процесс для вывода значений задержки в транскрипт process (strob) variable t1 : bit_vector(5 downto 0) := "101010"; begin -- process if strob'event and strob = '1' then -- write(OUTPUT, " " & time'image(now) & " " & to_string(x) & " " & to_string(y1) & " " & time'image(delay_y2)& " " & time'image(delay_y1) & LF ); write(OUTPUT, " " & to_string(x) & " " & to_string(y1) & " " & time'image(delay_y2)& " " & time'image(delay_y1) ); if y1 = y2 then All_Ok <= '1'; write(OUTPUT, " Ok" & LF); else All_Ok <= 'X'; write(OUTPUT, " FAIL" & LF); end if; end if; end process; end architecture tb2; |

| Рисунок 5 – Временная диаграмма тесбенча (sch01_tb(tb2)) |

|---|

Вывод в транскрипт:

# X Y DY2 DY1 # 000 00 9 ns 9 ns Ok # 001 00 0 ns 0 ns Ok # 010 00 0 ns 0 ns Ok # 011 01 0 ns 8 ns Ok # 100 11 7 ns 0 ns Ok # 101 00 5 ns 10 ns Ok # 110 11 5 ns 8 ns Ok # 111 01 5 ns 0 ns Ok # 000 00 0 ns 8 ns Ok # 001 00 0 ns 0 ns Ok # 010 00 0 ns 0 ns Ok # 011 01 0 ns 8 ns Ok # 100 11 7 ns 0 ns Ok # 101 00 5 ns 10 ns Ok # 110 11 5 ns 8 ns Ok # 111 01 5 ns 0 ns Ok # 000 00 0 ns 8 ns Ok

В результате моделирования получено, что максимальная задержка для

- DY1 = 10 нс (условных единиц)

- DY2 = 7 нс (условных единиц)

Начальное значение задержки (9 нс) для функции Y2 "фиктивное", поэтому в описании поведения сигнала delay_y2_max добавлена дополнительная строка обнуляющая delay_y2_max начальные 100 нс.

Однако, при ручном анализе схемы:

| |

|---|

| Рисунок 6 — Схема с отмеченным критическим путём для каждого выхода (Edit) |

Значение максимальной задержки равно 13 и 11 для выходов Y1 и Y2. Почему при моделировании не получены эти значения?