|

|

| Строка 1: |

Строка 1: |

| | {{ПЦУСБ TOC}} | | {{ПЦУСБ TOC}} |

| | + | {| align=center width=800px |

| | + | ! [[Файл:Проектирование.mm|center]] |

| | + | |} |

| | + | |

| | <!-- <graph> | | <!-- <graph> |

| | digraph G { | | digraph G { |

| Строка 29: |

Строка 33: |

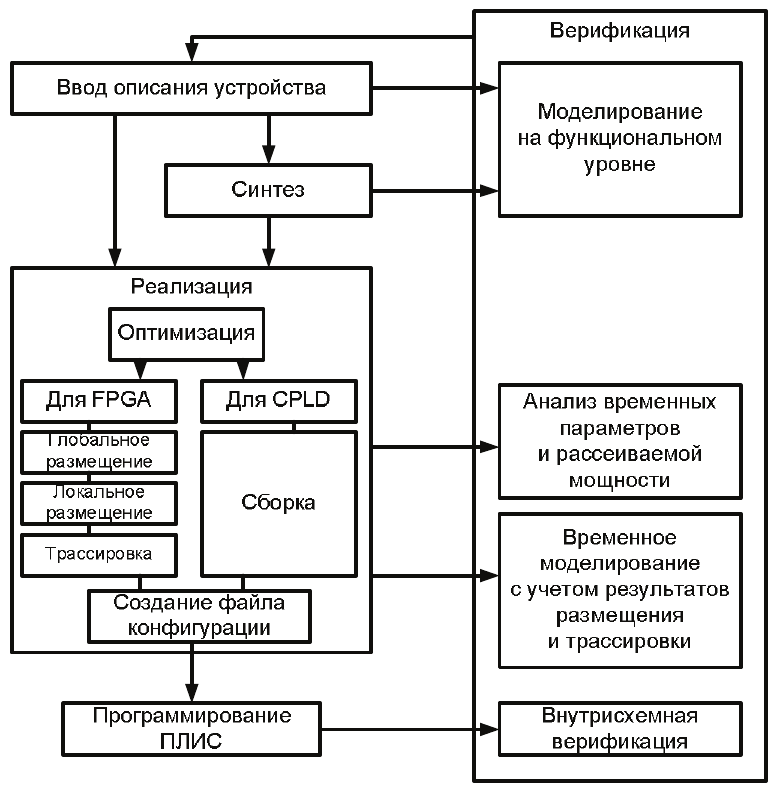

| | [[Файл:ISE flow.png|center]] | | [[Файл:ISE flow.png|center]] |

| | | | |

| − | == Слайд:Цели и задачи курса == | + | == Слайд: Немного мотивации == |

| − | Изучение методов алгоритмического, функционального и структурного описания цифровых систем на формальных языках проектирования, а также методов и компьютерных средств моделирования, верификации и схемной реализации проектов цифровых систем и устройств.

| + | |

| | | | |

| − | == Общая информация ==

| + | *''По запросу "vhdl OR verilog OR FPGA OR ПЛИС" на job.tut.by'' |

| − | Для оценки сложности интегральных схем используется единица эквивалентного вентиля (например 2-входовый И-НЕ), который соответствует 4-м эквивалентным транзисторам. Уровни интеграции СБИС принято делить на следующие группы:

| + | |

| − | * SSI - Small scale integration или МИС - малая интегральная схема с десятками и сотнями эквивалентных вентилей.

| + | |

| − | * MSI - Medium scale integration или СИС - средняя интегральная схема с тысячами вентилей.

| + | |

| − | * LSI - Large scale integration или БИС - большая интегральная схема с сотнями тысяч вентилей.

| + | |

| − | * VLSI – Very large scale integration или СБИС - Сверхбольшая Интегральная Схема с несколькими миллионами вентилей.

| + | |

| − | * USLI – Ultra large scale integration или УБИС - УльтраБольшая Интегральная Схема.

| + | |

| | | | |

| − | Наибольшее распространение на данный момент имеют СБИС, поэтому далее мы будем пользоваться этим термином для обозначения всех интегральных схем высокой степени интеграции.

| + | {| align=center |

| − | | + | ! Регион: |

| − | Кроме того интегральные схемы условно делятся на группы специализированных применений (ASIC - Application Specific Integrated Circuit) и коммерческие интегральные микросхемы общего применения, как массовые микропроцессоры и серийные наборы микросхем.

| + | ! ЗП: |

| − | С развитием технологий производства и повышением степени интеграции появилось такое понятие как системы на кристалле (СнК) или Systems-on-Chip (SoC), которые представляют собой комбинацию специализированных и универсальных процессорных ядер и блоков, выполненных на единой кремниевой подложке.

| + | ! Опыт |

| − | | + | |

| − | СБИС также различаются по полупроводниковой технологии исполнения:

| + | |

| − | * TTL или ТТЛ - транзисторно-транзисторная логика на биполярных транзисторах

| + | |

| − | * ECL или ЭСЛ - эмиттерно-связанная логика

| + | |

| − | * MOS - NMOS, CMOS или МОП, НМОП и КМОП логика.

| + | |

| − | | + | |

| − | === Слайд: Основные типы СБИС, используемые в электронной индустрии === | + | |

| − | * Полнозаказные СБИС (Full-Custom ASICs)

| + | |

| − | * Полузаказные матричные СБИС на основе стандартных ячеек-модулей (StandardCell–Based ASICs)

| + | |

| − | * Полузаказные СБИС на основе матрицы вентилей (Gate-Array–Based ASICs)

| + | |

| − | ** Канальные матрицы вентилей (Channeled Gate Array)

| + | |

| − | ** Бесканальные матрицы вентилей (Channelless Gate Array), наиболее популярные в настоящее время

| + | |

| − | ** Структурированные матрицы вентилей (Structured Gate Array)

| + | |

| − | * СБИС программируемой логики c макроячейками или макроблоками (Complex Programmable Logic Devices or CPLDs) или ПЛИС

| + | |

| − | * СБИС программируемой логики c микроячейками или базовыми блоками (FieldProgrammable Gate Arrays or FPGA)

| + | |

| − | | + | |

| − | Каждый тип СБИС имеет свою нишу на рынке, которая определяется массовостью применения приборов и изделий, а также степенью универсальности характеристик СБИС.

| + | |

| − | Все эти типы СБИС различаются стоимостью проектирования и изготовления, в случае ПЛИС разработчик использует готовые СБИС, программируя их для своих приложений, что дает минимальную цену подготовки производства, которую называют NRE – non-recurring engineering cost.<br>

| + | |

| − | На рисунке ниже приведены наборы масок (называемых также фотошаблонами) для полнозаказных и полузаказных СБИС, по их требуемому числу можно легко определить трудоемкость разработки каждого типа СБИС.<br>

| + | |

| − | Самые нижние маски определяют формирование базовых транзисторов на кремниевой подложке, следующие уровни определяют их топологические соединения металлическими проводниками для формирования базовых логических элементов и макро-блоков. Верхние уровни масок определяют межсоединения между крупными макроблоками (мега-элементами) и конфигурацию ввода-вывода. В современных технологических процессах производства полупроводников использутся свыше сорока масок, определяющих транзисторы, слои металлизации и изоляции. Стоимость комплекта масок достигает миллиона долларов и выше для процессов 45нм, а для 10нм достигает десятков миллионов долларов.

| + | |

| − | <br>

| + | |

| − | <center>[[Файл:Wafer masks.png|1200x900px|безрамки|Маски или фотошаблоны для полнозаказных (а) и полузаказных (b) СБИС]]</center><br>

| + | |

| − | <center>Маски или фотошаблоны для полнозаказных (а) и полузаказных (b) СБИС</center>

| + | |

| − | | + | |

| − | == Слайд: Маршрут проектирования ЦС ==

| + | |

| − | <graphviz>

| + | |

| − | digraph G {

| + | |

| − | node a[label="Техническое задание"]

| + | |

| − | node b[label="Спецификация"]

| + | |

| − | node c[label="верификация"]

| + | |

| − | node d[label="логическое проектирование"]

| + | |

| − | node e[label="физическое проектирование"]

| + | |

| − | a -> b

| + | |

| − | b -> c

| + | |

| − | b -> d

| + | |

| − | b -> e

| + | |

| − | d -> c

| + | |

| − | d -> e

| + | |

| − | }

| + | |

| − | </graphviz>

| + | |

| − | === Слайд: Логическое проектирование ===

| + | |

| − | Этап описания логических схем (не учитывается технология, физические,электрические и другие характеристики).

| + | |

| − | Описывается комбинационная логика, триггеры и связи между элементами схемы.

| + | |

| − | Для описания используются такие языки, как VHDL, Verilog, SystemC.

| + | |

| − | Результатом является логическая схема на уровне регистровых передач (RTL).

| + | |

| − | | + | |

| − | === Слайд: Верификация ===

| + | |

| − | Этап проверки соответствия описания логических схем спецификации.

| + | |

| − | Для целей верификации часто используются такие языки как SystemVerilog, SystemC, VHDL, specman E.

| + | |

| − | Для каждого из перечисленных языков существуют стандартные фреймворки (библиотеки).

| + | |

| − | * SystemVerilog: VMM, OVM, UVM.

| + | |

| − | * VHDL: OSVVM, UVVM.

| + | |

| − | * SystemC: UVM.

| + | |

| − | * Specman E: UVM.

| + | |

| − | | + | |

| − | === Слайд:Физическое проектирование ===

| + | |

| − | Этап построения топологии цифровой схемы (размещение логических элементов и проводников на поверхности кристалла) для конкретного технологического процесса с учётом всех производственных норм и характеристик Результатом является файл топологии интегральной схемы GDS II, который отправляется на фабрику.

| + | |

| − | | + | |

| − | == Слайд:Пример использования языков описания аппаратуры ==

| + | |

| − | {| align=center width=800px

| + | |

| − | ! [[Файл:Add1 .png|1200x900px|безрамки|Условное графическое представление одноразрядного сумматора]] | + | |

| | |- | | |- |

| − | ! [[Файл:Add1.png|1200x900px|безрамки|Одноразрядный сумматор]]

| + | |<hbarchart> |

| | + | Беларусь 10 |

| | + | Россия 70 |

| | + | Москва 28 |

| | + | Санкт-Петербург 25 |

| | + | </hbarchart> |

| | + | |<hbarchart> |

| | + | От 1.5K$ 40 |

| | + | От 2K$ 26 |

| | + | От 3K$ 22 |

| | + | От 4K$ 2 |

| | + | </hbarchart> |

| | + | |<hbarchart> |

| | + | От 3 до 6 лет 53 |

| | + | От 1 года до 3 лет 43 |

| | + | Нет опыта 21 |

| | + | </hbarchart> |

| | |} | | |} |

| − |

| |

| − |

| |

| − |

| |

| − |

| |

| − | <div style="width: 35%; float: left; margin: 0 0 5px 5px;">

| |

| − | [[Файл:Add1 .png|1200x900px|безрамки|Условное графическое представление одноразрядного сумматора]]

| |

| − | <br>

| |

| − | [[Файл:Add1.png|1200x900px|безрамки|Одноразрядный сумматор]]

| |

| − | </div>

| |

| − | <div style="width: 50%;float: right; margin: 0 0 5px 5px;">

| |

| − | Описание однобитного сумматора на языке VHDL

| |

| − | <source lang="vhdl">

| |

| − | entity add1 is

| |

| − | port (b1,b2 : in BIT;

| |

| − | c1,s1 : out BIT);

| |

| − | end add1;

| |

| − |

| |

| − | architecture struct_1 of add1 is

| |

| − | begin

| |

| − | s1<= ((b1 and (not b2)) or ((not b1) and b2));

| |

| − | c1<= b1 and b2;

| |

| − | end struct_1;

| |

| − | </source>

| |

| − | Описание однобитного сумматора на языке Verilog

| |

| − | <source lang="verilog">

| |

| − | module add1(input b1,b2;

| |

| − | output c1,s1);

| |

| − | assign s1 = ((b1 & ~b2) | (~b1 & b2);

| |

| − | assign c1 = b1 & b2;

| |

| − | endmodule

| |

| − | </source>

| |

| − | </div>

| |

| − | <br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br>

| |

| | | | |

| | == Слайд: NEW == | | == Слайд: NEW == |