ПЦУСБ/Лекция 3 — различия между версиями

Материал из Wiki

< ПЦУСБ

ANA (обсуждение | вклад) (→Слайд:Сложные логические функции) |

ANA (обсуждение | вклад) |

||

| Строка 179: | Строка 179: | ||

</source> | </source> | ||

|} | |} | ||

| + | |||

| + | |||

| + | === Слайд: [http://life-prog.ru/view_automati.php?id=14 Мультиплексор] === | ||

| + | |||

| + | * [http://g7iy34buhsdfn.narod.ru/4.htm комбинационная схема], которая передает сигнал с одного из информационных входов X<sub>i</sub> на единственный выход Y, причем номер выбираемого входа задается с помощью управляющих сигналов (адресных входов a<sub>i</sub>). | ||

| + | |||

| + | {| width=100% | ||

| + | ! http://de.ifmo.ru/--books/electron/tabl5.gif | ||

| + | |- | ||

| + | ! <big>y = OE(x0*~a1*~a0 + x1*~a1*a0 + x2*a1*~a0 + x3*a1*a0)</big> | ||

| + | |} | ||

| + | |||

| + | ==== Слайд:Мультиплексор (Схема) ==== | ||

| + | |||

| + | {| width=100% | ||

| + | ! http://life-prog.ru/articles3/6.htm1.gif | ||

| + | |- | ||

| + | ! http://digteh.ru/digital/image/MS_S.gif | ||

| + | |} | ||

| + | |||

| + | ==== Слайд:Мультиплексор (VHDL модель) ==== | ||

| + | |||

| + | <source lang="vhdl"> | ||

| + | entity mux is | ||

| + | |||

| + | port ( | ||

| + | x : in std_logic_vector(3 downto 0); | ||

| + | a : in std_logic_vector(1 downto 0); | ||

| + | y : out std_logic); | ||

| + | |||

| + | end mux; | ||

| + | |||

| + | architecture beh of mux is | ||

| + | begin | ||

| + | y <= | ||

| + | x(0) when a = "00" else | ||

| + | x(1) when a = "01" else | ||

| + | x(2) when a = "10" else | ||

| + | x(3) when a = "11" else | ||

| + | '0'; | ||

| + | end beh; | ||

| + | </source> | ||

| + | |||

| + | |||

| + | ==== Слайд:Мультиплексор (Особенность) ==== | ||

| + | |||

| + | * с помощью мультиплексора можно реализовать любую логическую функцию | ||

| + | |||

| + | {| width=100% | ||

| + | ! http://www.island-formoza.ru/images/arhitektura-pc-60.png | ||

| + | |} | ||

| + | |||

| + | ==== Слайд:Мультиплексор (Особенность) ==== | ||

| + | |||

| + | {| width=100% | ||

| + | ! http://life-prog.ru/articles3/6.htm8.jpg | ||

| + | |} | ||

| + | |||

| + | |||

| + | === Слайд: Демультиплексор [http://life-prog.ru/view_automati.php?id=14] [http://kursach37.com/uch_cifr_t4_45.html] === | ||

| + | |||

| + | * [http://g7iy34buhsdfn.narod.ru/4.htm комбинационная схема], которая выполняет функцию, обратную мультиплексору, т.е. в соответствии с принятой адресацией ''A<sub>i</sub>'' направляет информацию с единственного входа ''D'' на один из ''M'' выходов ''F<sub>j</sub>''. При этом на остальных выходах будут логические нули (единицы). | ||

| + | |||

| + | {| class=standard cellspacing="1" cellpadding="5" border="1" align=center | ||

| + | ! colspan="2" | Входы | ||

| + | ! colspan="4" | Выходы | ||

| + | |- | ||

| + | ! ''A''<sub>1</sub> | ||

| + | ! ''A''<sub>0</sub> | ||

| + | ! ''F''<sub>3</sub> | ||

| + | ! ''F''<sub>2</sub> | ||

| + | ! ''F''<sub>1</sub> | ||

| + | ! ''F''<sub>0</sub> | ||

| + | |- | ||

| + | | 0 | ||

| + | | 0 | ||

| + | | 0 | ||

| + | | 0 | ||

| + | | 0 | ||

| + | | ''D'' | ||

| + | |- | ||

| + | | 0 | ||

| + | | 1 | ||

| + | | 0 | ||

| + | | 0 | ||

| + | | ''D'' | ||

| + | | 0 | ||

| + | |- | ||

| + | | 1 | ||

| + | | 0 | ||

| + | | 0 | ||

| + | | ''D'' | ||

| + | | 0 | ||

| + | | 0 | ||

| + | |- | ||

| + | | 1 | ||

| + | | 1 | ||

| + | | ''D'' | ||

| + | | 0 | ||

| + | | 0 | ||

| + | | 0 | ||

| + | |} | ||

| + | |||

| + | |||

| + | ==== Слайд: Демультиплексор (Схема) ==== | ||

| + | |||

| + | {| width=100% align=center | ||

| + | ! http://kursach37.com/uch_cifr_t4_45_image016.gif | ||

| + | ! http://kursach37.com/uch_cifr_t4_45_image015.gif | ||

| + | ! http://kursach37.com/uch_cifr_t4_45_image017.gif | ||

| + | |} | ||

| + | |||

| + | ==== Слайд: Демультиплексор (VHDL модель) ==== | ||

| + | |||

| + | <source lang="vhdl"> | ||

| + | entity dms is | ||

| + | port ( | ||

| + | x : in std_logic; | ||

| + | a : in std_logic_vector(1 downto 0); | ||

| + | y : out std_logic_vector(3 downto 0)); | ||

| + | end dms; | ||

| + | |||

| + | architecture beh of dms is | ||

| + | begin | ||

| + | y <= | ||

| + | "000" & x when a = "00" else | ||

| + | "00" & x & '0' when a = "01" else | ||

| + | '0' & x & "00" when a = "10" else | ||

| + | x & "000" when a = "11" else | ||

| + | "0000"; | ||

| + | end beh; | ||

| + | </source> | ||

=== Слайд: END === | === Слайд: END === | ||

Версия 08:10, 20 сентября 2013

- Заголовок

- Базовые цифровые устройства

- Автор

- Авдеев Н.А.

- Нижний колонтитул

- ПЦУСБ/Лекция 3

- Дополнительный нижний колонтитул

- Авдеев Н.А., 08:44, 9 июня 2014

Содержание |

Слайд: Содержание

- Логические элементы (И, ИЛИ, НЕ, Исключающее ИЛИ)

- Комбинационные схемы:

- Дешифратор/Шифратор

- Мультиплексор/Демультиплексор

- Последовательные схемы

- Триггеры

- Регистры

- Автоматы

- Счетчики

Слайд: Логические элементы

В алгебре логики известны три основные логические операции:

- Логическое умножение (конъюнкция или операция И). Записывается как F = A Λ B, F = A & B, F = A·B, F = AB, читается – A и B.

- Логическое сложение (дизъюнкция или операция ИЛИ). Записывается как F = A V B, F = A | B, F = A+B, читается – F = A или B.

- Логическое отрицание (инверсия или операция НЕ). Записывается F = A , читается – F = “не” A.

Слайд:Таблица истинности логических элементов

| Аргументы | Логические операции (булевы функции) | ||||

|---|---|---|---|---|---|

| А | В | И | ИЛИ | НЕ | |

| A·B | A+B | A | B | ||

| 0 | 0 | 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 0 | 0 |

| Операторы VHDL | A and B | A or B | not A | not B | |

Комментарий

Таким образом, выполнение сколь угодно сложной логической операции может быть сведено к трем вышеперечисленным операциям. Следовательно, имея некоторые технические устройства, реализующие операции И, ИЛИ, НЕ, можно построить сколь угодно сложное цифровое устройство. Такие устройства называются соответственно логическими элементами И, ИЛИ, НЕ (рис. 2) и образуют основной базис или функционально полную систему логических элементов.

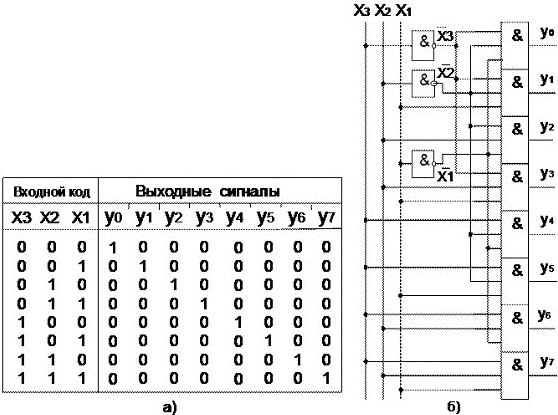

Слайд: Дешифратор (DC)

- комбинационная схема, преобразующее n-разрядный двоичныйв -ичный одноединичный (позиционный) код

|

|---|

Слайд:Дешифратор (VHDL модель)

entity dc is port ( x : in std_logic_vector(2 downto 0); y : out std_logic_vector(7 downto 0)); end dc; architecture beh of dc is begin y <= "00000001" when x = "000" else "00000010" when x = "001" else "00000100" when x = "010" else "00001000" when x = "011" else "00010000" when x = "100" else "00100000" when x = "101" else "01000000" when x = "110" else "10000000" when x = "111" else "00000000"; end beh;

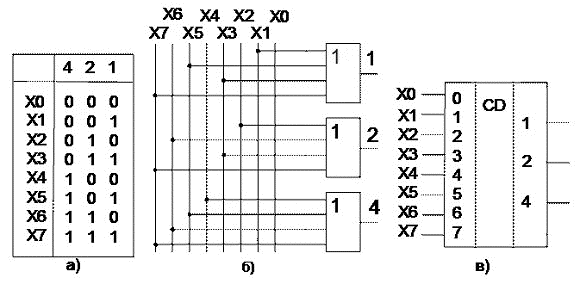

Слайд:Шифратор

- комбинационная схема, выполняющее преобразование одноединичный (позиционного) n-разрядного кода в m-разрядный двоичный код.

|

|---|

Слайд:Шифратор (VHDL модель 1)

| VHDL модель 1 | VHDL модель 2 |

|---|---|

entity cd is port ( x : in std_logic_vector(7 downto 0); y : out std_logic_vector(2 downto 0)); end dc; architecture beh1 of cd is begin y <= "000" when x(0) = "1" else "001" when x(1) = "1" else "010" when x(2) = "1" else "011" when x(3) = "1" else "100" when x(4) = "1" else "101" when x(5) = "1" else "110" when x(6) = "1" else "111" when x(7) = "1" else "000"; end beh1; |

entity cd is port ( x : in std_logic_vector(7 downto 0); y : out std_logic_vector(2 downto 0)); end dc; architecture beh2 of cd is begin y(0) <= x(1) or x(3) or x(5) or x(7); y(1) <= x(2) or x(3) or x(6) or x(7); y(2) <= x(4) or x(5) or x(6) or x(7); end beh2; |

Слайд: Мультиплексор

- комбинационная схема, которая передает сигнал с одного из информационных входов Xi на единственный выход Y, причем номер выбираемого входа задается с помощью управляющих сигналов (адресных входов ai).

|

|---|

| y = OE(x0*~a1*~a0 + x1*~a1*a0 + x2*a1*~a0 + x3*a1*a0) |

Слайд:Мультиплексор (Схема)

|

|---|

|

Слайд:Мультиплексор (VHDL модель)

entity mux is port ( x : in std_logic_vector(3 downto 0); a : in std_logic_vector(1 downto 0); y : out std_logic); end mux; architecture beh of mux is begin y <= x(0) when a = "00" else x(1) when a = "01" else x(2) when a = "10" else x(3) when a = "11" else '0'; end beh;

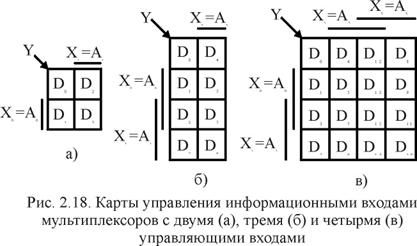

Слайд:Мультиплексор (Особенность)

- с помощью мультиплексора можно реализовать любую логическую функцию

|

|---|

Слайд:Мультиплексор (Особенность)

|

|---|

Слайд: Демультиплексор [1] [2]

- комбинационная схема, которая выполняет функцию, обратную мультиплексору, т.е. в соответствии с принятой адресацией Ai направляет информацию с единственного входа D на один из M выходов Fj. При этом на остальных выходах будут логические нули (единицы).

| Входы | Выходы | ||||

|---|---|---|---|---|---|

| A1 | A0 | F3 | F2 | F1 | F0 |

| 0 | 0 | 0 | 0 | 0 | D |

| 0 | 1 | 0 | 0 | D | 0 |

| 1 | 0 | 0 | D | 0 | 0 |

| 1 | 1 | D | 0 | 0 | 0 |

Слайд: Демультиплексор (Схема)

|

|

|

|---|

Слайд: Демультиплексор (VHDL модель)

entity dms is port ( x : in std_logic; a : in std_logic_vector(1 downto 0); y : out std_logic_vector(3 downto 0)); end dms; architecture beh of dms is begin y <= "000" & x when a = "00" else "00" & x & '0' when a = "01" else '0' & x & "00" when a = "10" else x & "000" when a = "11" else "0000"; end beh;