ПТСиПЦУвСБ/Практическая работа 4

Материал из Wiki

Лекции ПТСиПЦУвСБ

Лекции

Практические

- Практическая работа 1

- Практическая работа 2

- Практическая работа 3

- Практическая работа 4

Тесты

Лабораторные

Доп. материалы

Содержание |

Доступное оборудование

Варианты заданий

Уровень сложности 0

Задание 1-1

- Разработать синтезируемое VHDL-описание блока кодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

- Тип выходной кодировки 1-256 (iso-15693-2) Файл:ISO15693-2.pdf

- Частота тактового сигнала 13.56 MHz

- Перед стартом передачи данных посылать SOF

- После завершения передачи данных EOF

Задание 1-2

- Разработать синтезируемое VHDL-описание блока декодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных. (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок записи принимаемых данных в файл.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

- Тип входной кодировки 1-256 (iso-15693-2) Файл:ISO15693-2.pdf

- Частота тактового сигнала 13.56 MHz

- Прием данных начинать после получения SOF

- Прекращать прием после прихода символа EOF

Задание 2-1

- Разработать синтезируемое VHDL-описание блока кодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

- Тип выходной кодировки 1-256 (iso-15693-2) Файл:ISO15693-2.pdf

- Частота тактового сигнала 13.56 MHz

- Перед стартом передачи данных посылать SOF

- После завершения передачи данных EOF

Задание 2-2

- Разработать синтезируемое VHDL-описание блока декодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных. (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок записи принимаемых данных в файл.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

- Тип выходной кодировки 1-256 (iso-15693-2) Файл:ISO15693-2.pdf

- Частота тактового сигнала 13.56 MHz

- Перед стартом передачи данных посылать SOF

- После завершения передачи данных EOF

Задание 3-1

- Разработать синтезируемое VHDL-описание блока кодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

- Тип выходной кодировки 1-256 (iso-15693-2) Файл:ISO15693-2.pdf

- Частота тактового сигнала 13.56 MHz

- Перед стартом передачи данных посылать SOF

- После завершения передачи данных EOF

Задание 3-2

- Разработать синтезируемое VHDL-описание блока декодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных. (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок записи принимаемых данных в файл.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

- Тип входной кодировки 1-256 (iso-15693-2) Файл:ISO15693-2.pdf

- Частота тактового сигнала 13.56 MHz

- Прием данных начинать после получения SOF

- Прекращать прием после прихода символа EOF

Задание 4-1

- Разработать синтезируемое VHDL-описание блока кодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Выходной порт DATA_O, для выдачи закодированных данных

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

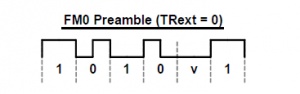

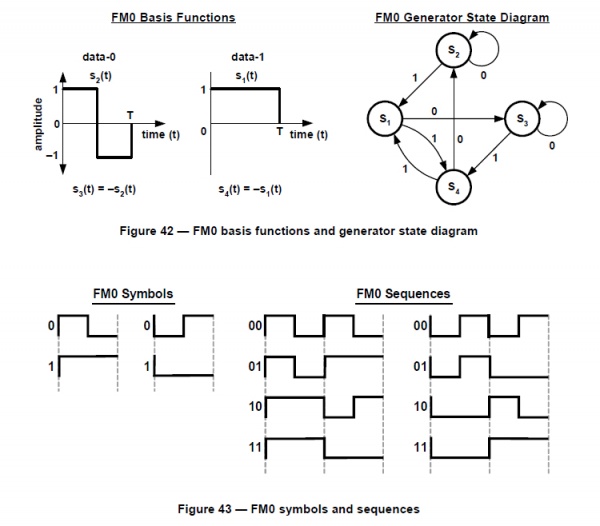

- Тип выходной кодировки FM0 (iso-18000-6) Файл:ISO18000-6REV1v62.pdf

- Число передаваемых данных задается generic паратмером NUM_SEND_BIT

- Частота тактового сигнала 1.98 MHz

- Частота закодированных данных 640 KHz

- Перед стартом передачи данных посылать SOF

- После завершения передачи данных, посылать EOF

Задание 4-2

- Разработать синтезируемое VHDL-описание блока декодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных. (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок записи принимаемых данных в файл.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

- Тип входной кодировки 1-256 (iso-18000-6) Файл:ISO18000-6REV1v62.pdf

- Число принимаемых данных задается в generic параметре NUM_GET_BIT!

- Частота тактового сигнала 1.92 MHz

- Частота закодированных данных 640 KHz

- Прием данных начинать после получения SOF

- Прекращать прием после прихода символа EOF или после получения заданного числа бит.

Задание 5-1

- Разработать синтезируемое VHDL-описание блока кодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Выходной порт DATA_O, для выдачи закодированных данных

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

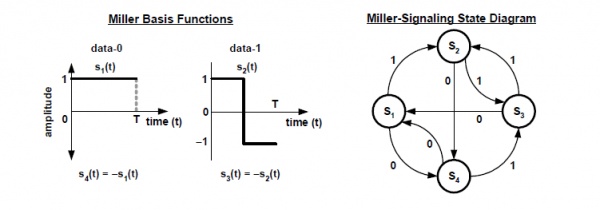

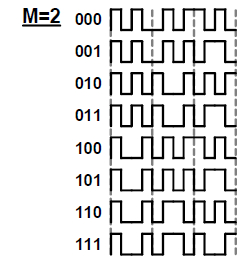

- Тип выходной кодировки код Миллера (iso-18000-6) Файл:ISO18000-6REV1v62.pdf

- Число передаваемых данных задается в generic параметре NUM_SEND_BIT !

- Частота тактового сигнала 1.98 MHz

- Частота закодированных данных 320 KHz (два такта выходной частоты на один бит данных, см. рис.)

- Перед стартом передачи данных посылать SOF

- После завершения передачи данных посылать EOF

Задание 5-2

- Разработать синтезируемое VHDL-описание блока декодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных. (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок записи принимаемых данных в файл.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Входной порт DATA_I, для принимаемых от кодера данных

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

- Тип входной кодировки код Миллера (iso-18000-6) Файл:ISO18000-6REV1v62.pdf

- Число принимаемых данных задается в generic параметре NUM_GET_BIT!

- Частота тактового сигнала 1.98 MHz

- Частота закодированных данных 320 KHz (два такта выходной частоты на один бит данных, см. рис.)

- Прием данных начинать после получения SOF

- Прекращать прием после прихода символа EOF или после приема NUM_GET_BIT

Задание 6-1

- Разработать синтезируемое VHDL-описание блока кодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Выходной порт DATA_O, для выдачи закодированных данных

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

- Тип выходной кодировки iso-18000-6 Файл:Input 18000-6 (E)REV1 v62.pdf

- Число передаваемых данных задается в generic параметре NUM_SEND_BIT !

- Частота тактового сигнала 8 MHz

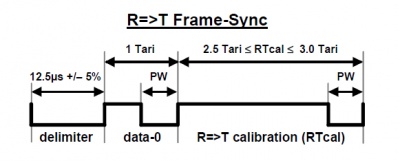

- Tari= 6.25us (см. рис.)

- RTcal= (Data-0) + (Data-1)=3 * Tari = 18.75us

- Перед стартом передачи данных посылать SOF

- Завершение передачи данных после посылки NUM_SEND_BIT бит данных.

Задание 6-2

- Разработать синтезируемое VHDL-описание блока кодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Входной порт DATA_I, для принимаемых от кодера данных

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

- Тип входной кодировки iso-18000-6 Файл:Input 18000-6 (E)REV1 v62.pdf

- Число принимаемых данных задается в generic параметре NUM_GET_BIT!

- Частота тактового сигнала 1.92 MHz

- Tari= 6.25us (см. рис.)

- RTcal= (Data-0) + (Data-1)=3 * Tari = 18.75us

- Данные декодировать после получения SOF

- Полученный символ кодирует 1, если его длинна больше RTcal/2, если меньше, то кодирует логический 0.

- Завершение передачи данных после посылки NUM_SEND_BIT бит данных.

Задание 7-1

- Разработать синтезируемое VHDL-описание блока кодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Выходной порт DATA_O, для выдачи закодированных данных

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

- Тип выходной кодировки ATA-5575 Файл:Doc9167.pdf

- Число передаваемых данных задается в generic параметре NUM_SEND_BIT !

- Частота тактового сигнала 125 КHz

- Для кодирования данных смотри таблицу

- Старт передачи данных - первая пауза.

- Завершение передачи данных после посылки NUM_SEND_BIT бит данных.

Задание 7-2

- Разработать синтезируемое VHDL-описание блока декодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Выходной порт DATA_O, для выдачи закодированных данных

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

- Тип входной кодировки ATA-5575 Файл:Doc9167.pdf

- Число передаваемых данных задается в generic параметре NUM_SEND_BIT !

- Частота тактового сигнала 125 КHz

- Для декодирования данных смотри таблицу

- Старт приема данных - первая пауза D_I равен 0.

- Завершение приема данных после получения NUM_SEND_BIT бит данных.

Уровень сложности 1

- Преобразователь 8-ми разрядного числа из двоичного кода в двоично-десятичный код с отображением на семисегментном индикаторе в десятичном виде

- a) Преобразователь 10-разрядного числа из двоичного кода в двоично-десятичный код с отображением на 4-х позиционном семисегментном индикаторе в десятичном виде с последовательным вводом двоичного числа.

- Преобразователь числа из двоично-десятичного кода в 8-ми разрядный двоичный код с отображением на линейке светодиодов

- входной код отображается на семисегментном индикаторе в десятичном виде

- выходной код отображается на линейке светодиодов

- Калькулятор (4-разрядное число [×|+|-] 4-разрядное число)

- значения входных аргументов задаётся переключателями, при этом эти значения отображаются в шестнадцатеричном виде на семисегментном индикаторе (первых два индикатора)

- значение результата вычислений отображается в шестнадцатеричном виде на семисегментном индикаторе (вторые 2 индикатора)

- выполняемая арифметическая операция задаётся кнопками, при этом на светодиодах фиксируется номер операции.

- часы с выводом на семисегментный индикатор.

- таймер с выводом на семисегментный индикатор.

- секундомер с выводом на семисегментный индикатор.

Уровень сложности 2

- Функция "Эхо" для терминала. Т.е. получение байта с компьютера по RS232 и отправка его обратно в ПК.

- Отобразить на экране монитора шахматную доску через VGA интерфейс.

- Термометр на основе температурного сенсора (DS18B20, 1-WIRE) с выводом значения на семисегментный индикатор либо на ЖКИ дисплей.

- Калькулятор с клавиатурой (матрица 4×4 кнопки) с отображением на светодиодном (4-х позицонном) или ЖКИ дисплее:

- Операции (+|–|÷|×|...) над целыми числами;

- Операции (+|–|÷|×|...) над целыми и вещественными числами;

- Тригонометрические операции (sin|cos|tg|ctg|...) над целыми и вещественными числами;

- Редактор текста с вводом с клавиатуры (PS/2)

- с выводом на ЖКИ дисплей LCD12864 (128×64 пикселей);

- с выводом в терминал по протоколу RS232.

- часы реального времени (PCF8563 RTC Board) с выводом на семисегментный индикатор либо на ЖКИ дисплей.

- дополнительные функции: таймер, секундомер, будильник и др.

Уровень сложности 3

- Калькулятор ([×|+|-]) в терминале. Задание входных и выходных данных и кода операции по интерфейсу RS232. (Например, набираешь в терминале "2+8=", после набора символа '=' из ПЛИС возвращается результат выражения.

- Отобразить на экране монитора надпись "ПЦУСБ" через VGA интерфейс.