Проектирование цифровых систем на языках описания аппаратуры/Лекция 17

Материал из Wiki

- Заголовок

- Примеры описаний схем для FPGA на отладочной плате с FPGA фирмы Xilinx

- Автор

- Ланкевич Ю.Ю.

- Нижний колонтитул

- Проектирование цифровых систем на языках описания аппаратуры/Лекция 17

- Дополнительный нижний колонтитул

- Ланкевич Ю.Ю., 02:34, 30 ноября 2020

Содержание |

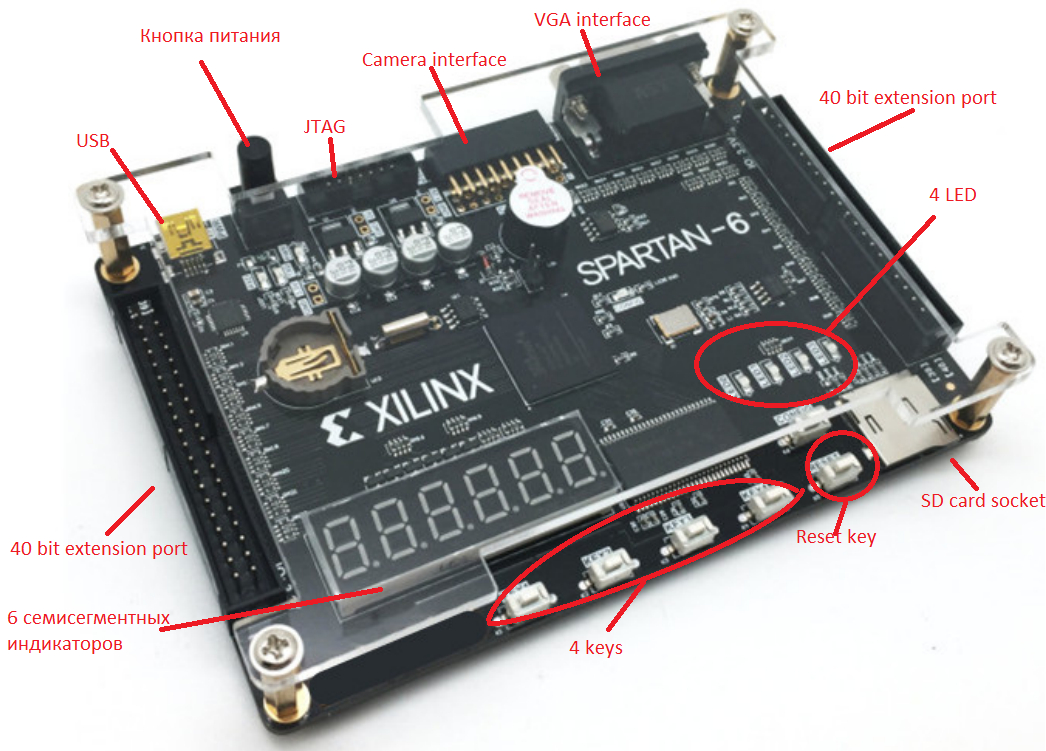

Слайд:Описание сипользуемой отладочной платы и модулей расширений

На отладочной плате имеются следующие коспоненты:

- ПЛИС FPGA Xilinx xc6slx9-2ftg256

- USB interface

- USB to UART

- 50M Crystal oscillator

- 256 Mbit SDRAM

- Real Time Clock(RTC) I2C

- 2x 40-pin extension ports

- 6 digit digital tube (6 семисегментных индикаторов)

- 4 LED

- 65536 color VGA interface

- Buzzer

- SD card socket

- Camera interface

- EEPROM

Ресурсы FPGA:

| Характеристика | XC6SLX9 |

|---|---|

| Slices | 1430 |

| BRAM | 32 |

| DSP | 16 |

| IO, max | 200 |

| CMT | 2 |

Слайд:Пример 1. ТЗ

Входной интерфейс: UART приемник. Выходной интерфейс UART передатчик.

Модуль должен уметь принимать и интерпретировать комманды с компьютера и отправлять данные обратно. Модуль должен быть расширяемым, чтобы была возможность работать с пользовательским интерфейсом.

Вопросы:

- В каком формате приходят команды по UART (В виде некоторого кода, либо в виде текста (ASCII), который надо интерпретировать?

- Как должен выглядеть пользовательский интерфейс?

- UART передаёт сырые данные, без предобработки

- Какие дополнительные функции могли бы быть полезными

a) Должен уметь отправлять хосту системные сообщения: занят/не готов принимать комманды и данные, не занят/готов, начало передачи данных, конец передачи данных

b) Во время передачи данных все команды игнорируются

c) загрузка начальных данных в память?

d) ??

Слайд:Пример 1. Спецификация

Слайд:Пример 1. VHDL описание

Слайд:Пример 1. Синтез

TODO:

- ISE Core generator

- ISE Language tamplates

- Plan Ahead

- Pins mapping

- Timing constraints

- FPGA programming via JTAG