Проектирование цифровых систем на языках описания аппаратуры — различия между версиями

Материал из Wiki

Yura (обсуждение | вклад) |

Yura (обсуждение | вклад) |

||

| Строка 1: | Строка 1: | ||

{{ПЦСЯОА TOC}} | {{ПЦСЯОА TOC}} | ||

__NOTOC__ | __NOTOC__ | ||

| − | + | == Цели и задачи курса == | |

Изучение методов алгоритмического, функционального и структурного описа-ния цифровых систем на формальных языках проектирования, а также методов и компьютерных средств моделирования, верификации и схемной реализации проектов цифровых систем и устройств. | Изучение методов алгоритмического, функционального и структурного описа-ния цифровых систем на формальных языках проектирования, а также методов и компьютерных средств моделирования, верификации и схемной реализации проектов цифровых систем и устройств. | ||

| − | + | == Маршрут проектирования ЦС == | |

<graphviz> | <graphviz> | ||

digraph G { | digraph G { | ||

| Строка 24: | Строка 24: | ||

* физическое проектирование - этап построения топологии цифровой схемы (размещение логических элементов и проводников на поверхности кристалла) для конкретного технологического процесса с учётом всех производственных норм и характеристик Результатом является файл топологии интегральной схемы GDS II, который отправляется на фабрику. | * физическое проектирование - этап построения топологии цифровой схемы (размещение логических элементов и проводников на поверхности кристалла) для конкретного технологического процесса с учётом всех производственных норм и характеристик Результатом является файл топологии интегральной схемы GDS II, который отправляется на фабрику. | ||

| − | + | == Где и для чего используются языки описания аппаратуры == | |

<div style="width: 35%; float: left; margin: 0 0 5px 5px;"> | <div style="width: 35%; float: left; margin: 0 0 5px 5px;"> | ||

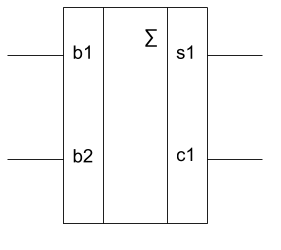

[[Файл:Add1 .png|1200x900px|безрамки|Условное графическое представление одноразрядного сумматора]] | [[Файл:Add1 .png|1200x900px|безрамки|Условное графическое представление одноразрядного сумматора]] | ||

| Строка 31: | Строка 31: | ||

</div> | </div> | ||

<div style="width: 50%;float: right; margin: 0 0 5px 5px;"> | <div style="width: 50%;float: right; margin: 0 0 5px 5px;"> | ||

| − | + | Описание однобитного сумматора на языке VHDL | |

| − | + | <source lang="vhdl"> | |

| − | + | entity add1 is | |

| − | + | port (b1,b2 : in BIT; | |

| − | + | c1,s1 : out BIT); | |

| − | + | end add1; | |

| − | + | ||

| − | + | architecture struct_1 of add1 is | |

| − | + | begin | |

| − | + | s1<= ((b1 and (not b2)) or ((not b1) and b2)); | |

| + | c1<= b1 and b2; | ||

| + | end struct_1; | ||

| + | </source> | ||

</div> | </div> | ||

<br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br> | <br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br> | ||

Версия 21:27, 29 августа 2020

Лекции ПЦСЯОА

Лекции

Практические

Доп. материалы

Цели и задачи курса

Изучение методов алгоритмического, функционального и структурного описа-ния цифровых систем на формальных языках проектирования, а также методов и компьютерных средств моделирования, верификации и схемной реализации проектов цифровых систем и устройств.

Маршрут проектирования ЦС

- логическое проектирование - этап описания логических схем (не учитывается технология, физические,электрические и другие характеристики). Результатом является логическая схема на уровне регистровых передач (RTL).

- верификация - этап проверки соответствия описания логических схем спецификации

- физическое проектирование - этап построения топологии цифровой схемы (размещение логических элементов и проводников на поверхности кристалла) для конкретного технологического процесса с учётом всех производственных норм и характеристик Результатом является файл топологии интегральной схемы GDS II, который отправляется на фабрику.

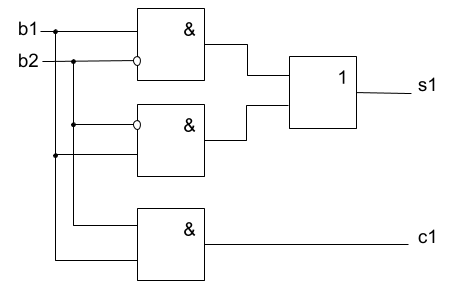

Где и для чего используются языки описания аппаратуры

Описание однобитного сумматора на языке VHDL

entity add1 is port (b1,b2 : in BIT; c1,s1 : out BIT); end add1; architecture struct_1 of add1 is begin s1<= ((b1 and (not b2)) or ((not b1) and b2)); c1<= b1 and b2; end struct_1;

Обратная связь

- (a) yurafreedom18@gmail.com

Маршрут проектирования ЦС