Проектирование цифровых систем на языках описания аппаратуры — различия между версиями

Yura (обсуждение | вклад) |

Yura (обсуждение | вклад) |

||

| Строка 20: | Строка 20: | ||

} | } | ||

</graphviz> | </graphviz> | ||

| − | + | === Логическое проектирование === | |

| − | + | Этап описания логических схем (не учитывается технология, физические,электрические и другие характеристики). Результатом является логическая схема на уровне регистровых передач (RTL). | |

| − | + | ||

| − | == | + | === Верификация === |

| + | Этап проверки соответствия описания логических схем спецификации. | ||

| + | Для целей верификации часто используются такие языки как SystemVerilog, SystemC, VHDL, specman E. | ||

| + | Для каждого из перечисленных языков существуют стандартные фреймворки (библиотеки). | ||

| + | * SystemVerilog: VMM, OVM, UVM. | ||

| + | * VHDL: OSVVM, UVVM. | ||

| + | * SystemC: UVM. | ||

| + | * Specman E: UVM. | ||

| + | |||

| + | === Физическое проектирование === | ||

| + | Этап построения топологии цифровой схемы (размещение логических элементов и проводников на поверхности кристалла) для конкретного технологического процесса с учётом всех производственных норм и характеристик Результатом является файл топологии интегральной схемы GDS II, который отправляется на фабрику. | ||

| + | |||

| + | == Пример использования языков описания аппаратуры == | ||

<div style="width: 35%; float: left; margin: 0 0 5px 5px;"> | <div style="width: 35%; float: left; margin: 0 0 5px 5px;"> | ||

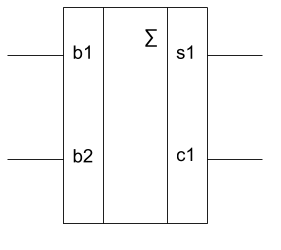

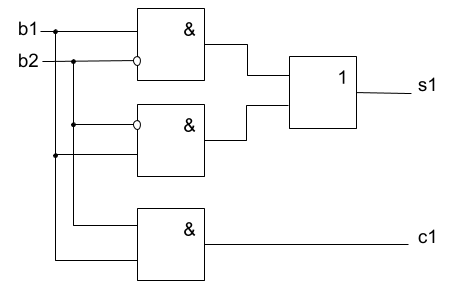

[[Файл:Add1 .png|1200x900px|безрамки|Условное графическое представление одноразрядного сумматора]] | [[Файл:Add1 .png|1200x900px|безрамки|Условное графическое представление одноразрядного сумматора]] | ||

Версия 21:43, 29 августа 2020

Цели и задачи курса

Изучение методов алгоритмического, функционального и структурного описа-ния цифровых систем на формальных языках проектирования, а также методов и компьютерных средств моделирования, верификации и схемной реализации проектов цифровых систем и устройств.

Маршрут проектирования ЦС

Логическое проектирование

Этап описания логических схем (не учитывается технология, физические,электрические и другие характеристики). Результатом является логическая схема на уровне регистровых передач (RTL).

Верификация

Этап проверки соответствия описания логических схем спецификации. Для целей верификации часто используются такие языки как SystemVerilog, SystemC, VHDL, specman E. Для каждого из перечисленных языков существуют стандартные фреймворки (библиотеки).

- SystemVerilog: VMM, OVM, UVM.

- VHDL: OSVVM, UVVM.

- SystemC: UVM.

- Specman E: UVM.

Физическое проектирование

Этап построения топологии цифровой схемы (размещение логических элементов и проводников на поверхности кристалла) для конкретного технологического процесса с учётом всех производственных норм и характеристик Результатом является файл топологии интегральной схемы GDS II, который отправляется на фабрику.

Пример использования языков описания аппаратуры

entity add1 is port (b1,b2 : in BIT; c1,s1 : out BIT); end add1; architecture struct_1 of add1 is begin s1<= ((b1 and (not b2)) or ((not b1) and b2)); c1<= b1 and b2; end struct_1;

Обратная связь

- (a) yurafreedom18@gmail.com

Маршрут проектирования ЦС