Лекции

Практические

Лабораторные

Табель

Доп. материалы

- Заголовок

- Цифровые блоки RFID

- Автор

- Зайцев В.С.

- Нижний колонтитул

- Спец курс (Избранные главы VHDL)/Реализация описания цифровых блоков RFID-меток

- Дополнительный нижний колонтитул

- Зайцев В.С., 13:16, 2 декабря 2013

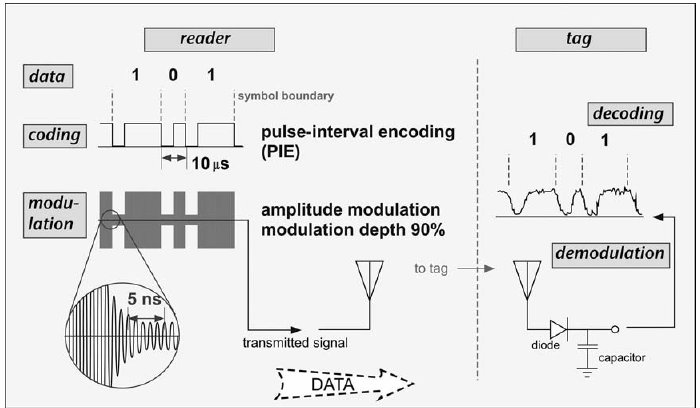

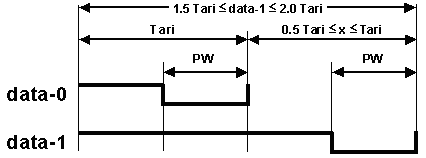

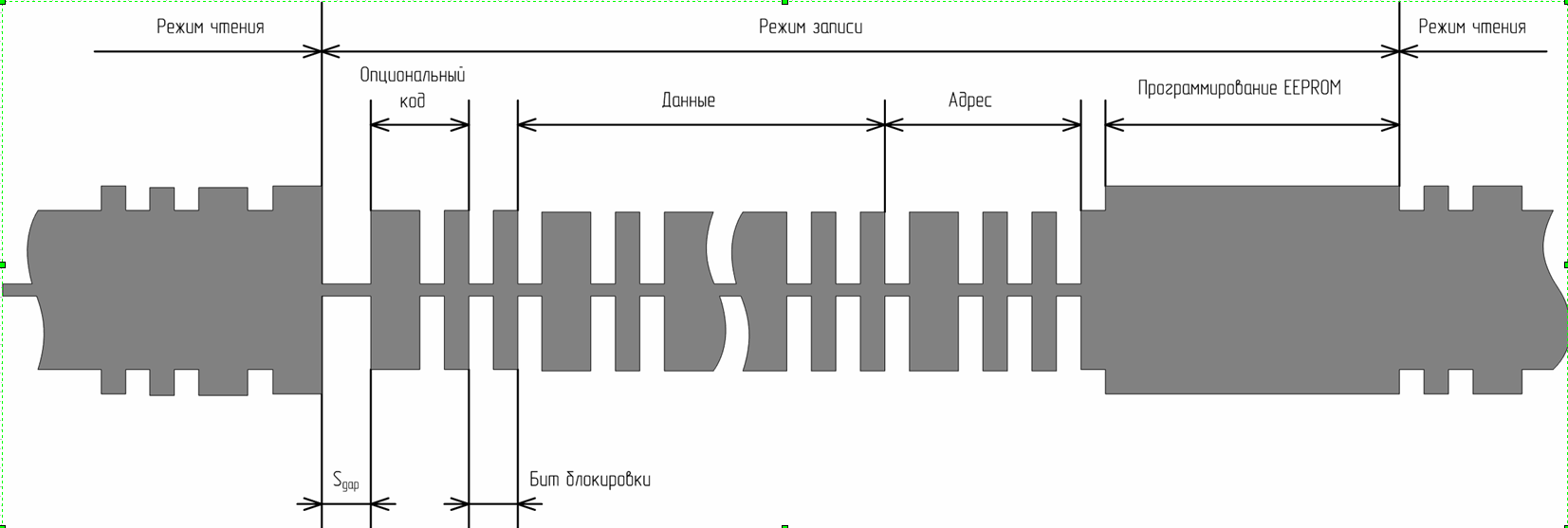

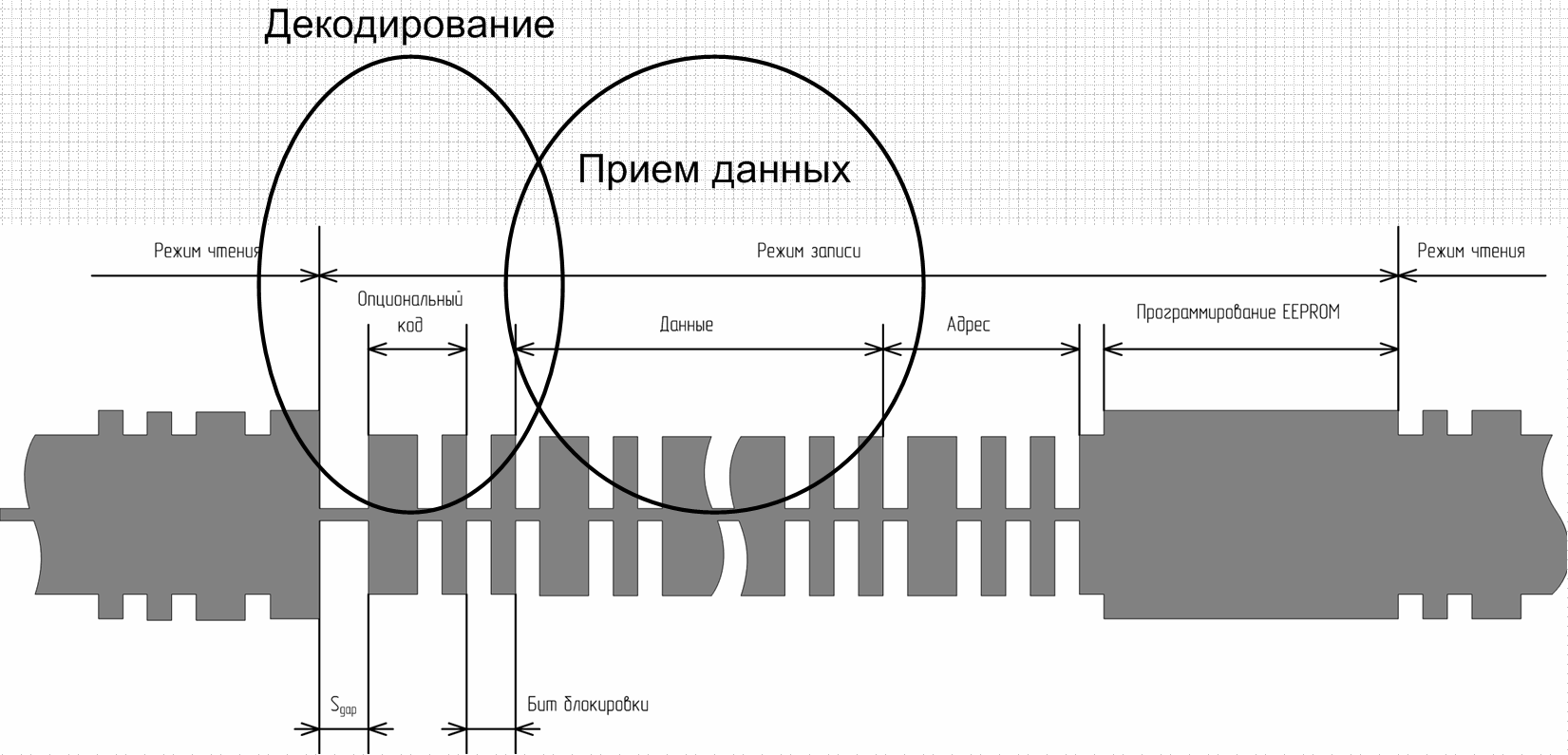

Слайд: Блок декодирования

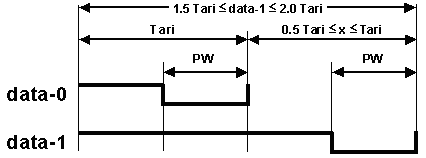

Слайд: Входные последовательности

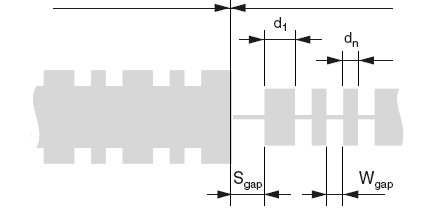

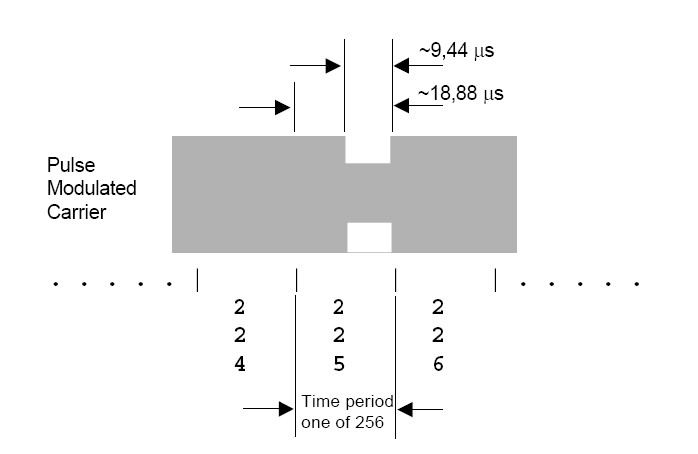

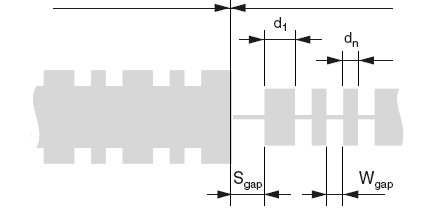

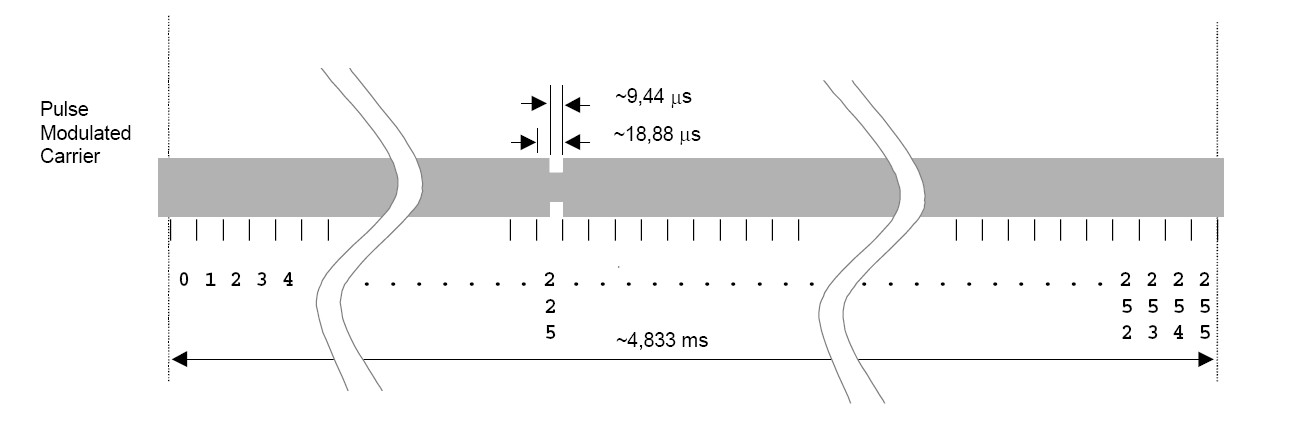

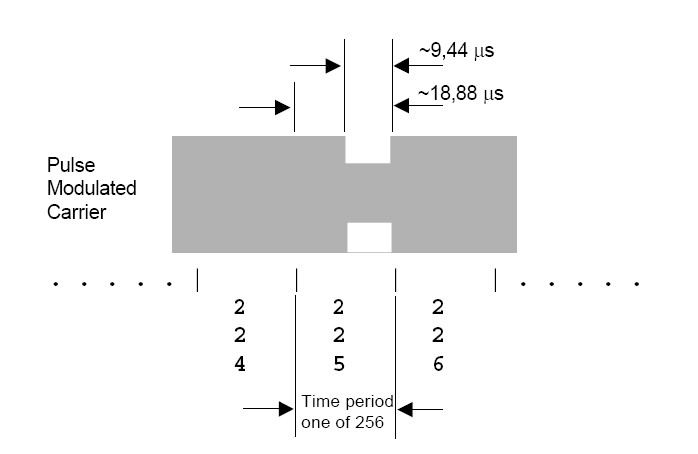

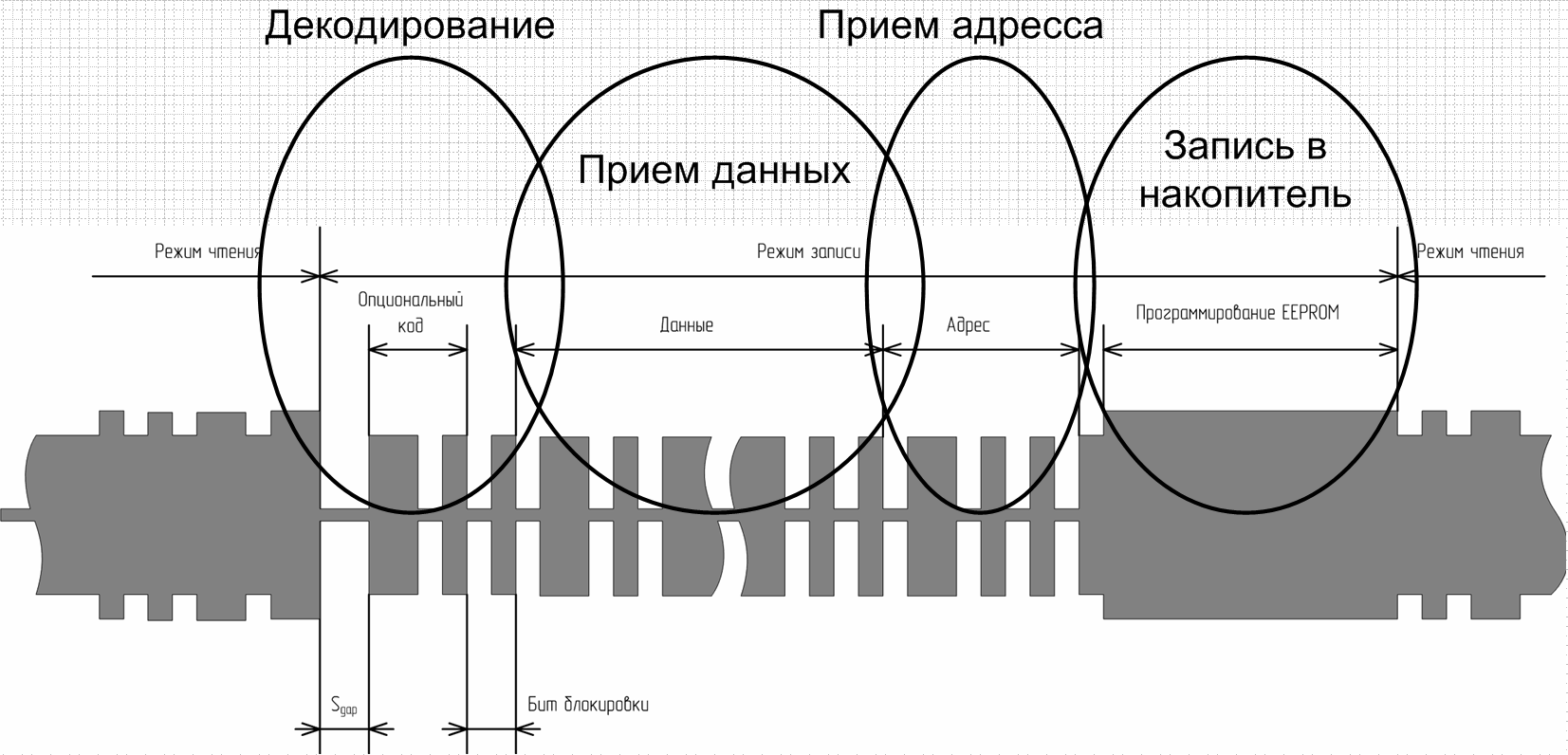

Протокол записи и чтения данных ISO11784/785

|

| Параметр

|

Примечание

|

Обозначение

|

не менее

|

не более

|

Единица

|

| Стартовый интервал

|

|

Sgap

|

10

|

50

|

периодов частоты

|

| Интервал между данными

|

в режиме записи

|

Wgap

|

8

|

30

|

периодов частоты

|

| Запись данных в обычном режиме

|

данные «0»

|

d0

|

16

|

31

|

периодов частоты

|

| данные «1»

|

d1

|

48

|

63

|

периодов частоты'

|

|

architecture beh of decoder is

signal count : unsignaed (8 downto 0);

begin -- beh

rst <= dm;

aa: process (clk, rst)

begin -- process aa

if rst = '0' then

count <= (others => '0');

get_data <= '0';

elsif clk'event and clk = '1' then

count <= count + 1;

if 8 < count and count < 16 then

get_data <= '0';

elsif 48 < count and count < 63 then

get_data <= '1';

else

get_data <= '0';

end if;

end if;

end process aa;

end beh; |

|

|

architecture beh of decoder is

signal count : unsignaed (8 downto 0);

signal dmi : std_logic;

signal dmij : std_logic;

signal delimiter : unsigned (8 downto 0);

signal tari : unsigned (8 downto 0);

signal rtcal : unsigned (8 downto 0);

begin -- beh

rst_c <= rst or rst_count_when_end_pause;

aa : process (clk, rst_c)

begin -- process aa

if rst_c = '1' then

count <= (others => '0');

get_data <= '0';

elsif clk'event and clk = '1' then

count <= count + 1;

if first_pause then

delimiter <= count;

elsif second_pause then

tari <= count;

elsif 3_pause then

rtcal <= count;

elsif next_pause then

if count > rtcal_div_2 then

get_data <= '1';

else

get_data <= '0';

end if;

end if;

end if;

end process aa;

end beh; |

|

|

architecture beh of decoder is

signal count : unsignaed (7 downto 0);

signal count_bit : unsignaed (7 downto 0);

begin -- beh

aa: process (clk, rst)

begin -- process aa

if rst = '0' then

count <= (others => '0');

get_data_byte <= '0';

elsif clk'event and clk = '1' then

count <= count + 1;

if count = div_freq then

count <= x"00";

count_bit <= count_bit + '1';

if dm = '0' then

get_data_byte <= count_bit;

end if;

end if;

end if;

end process aa;

end beh; |

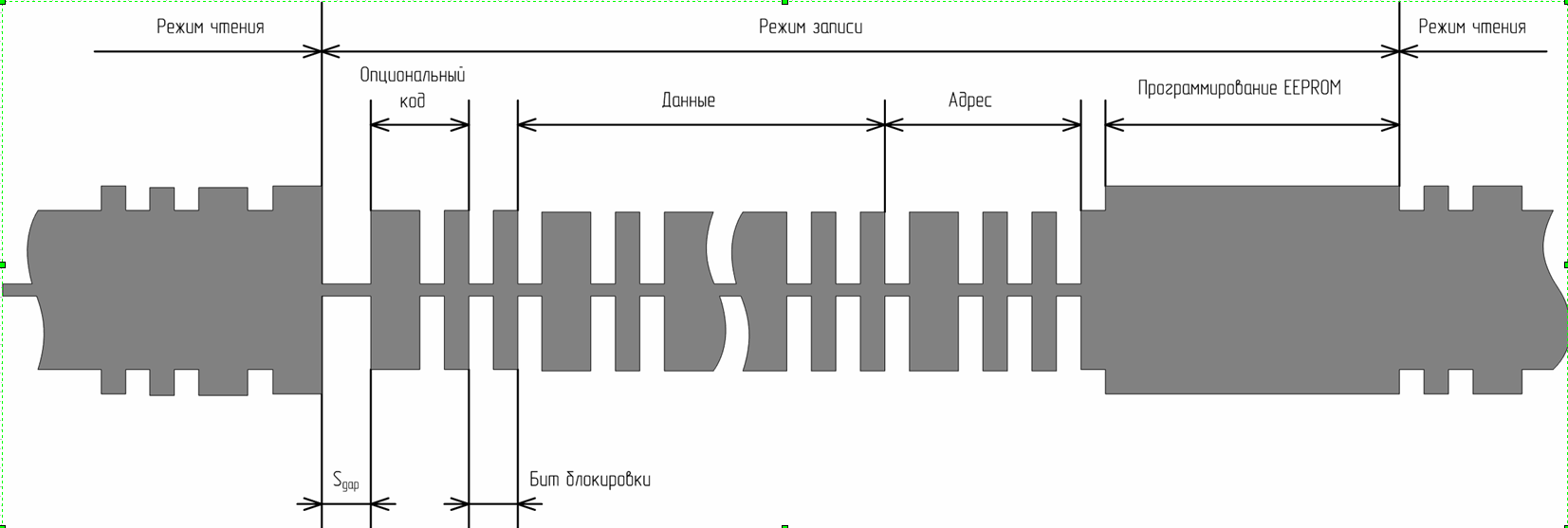

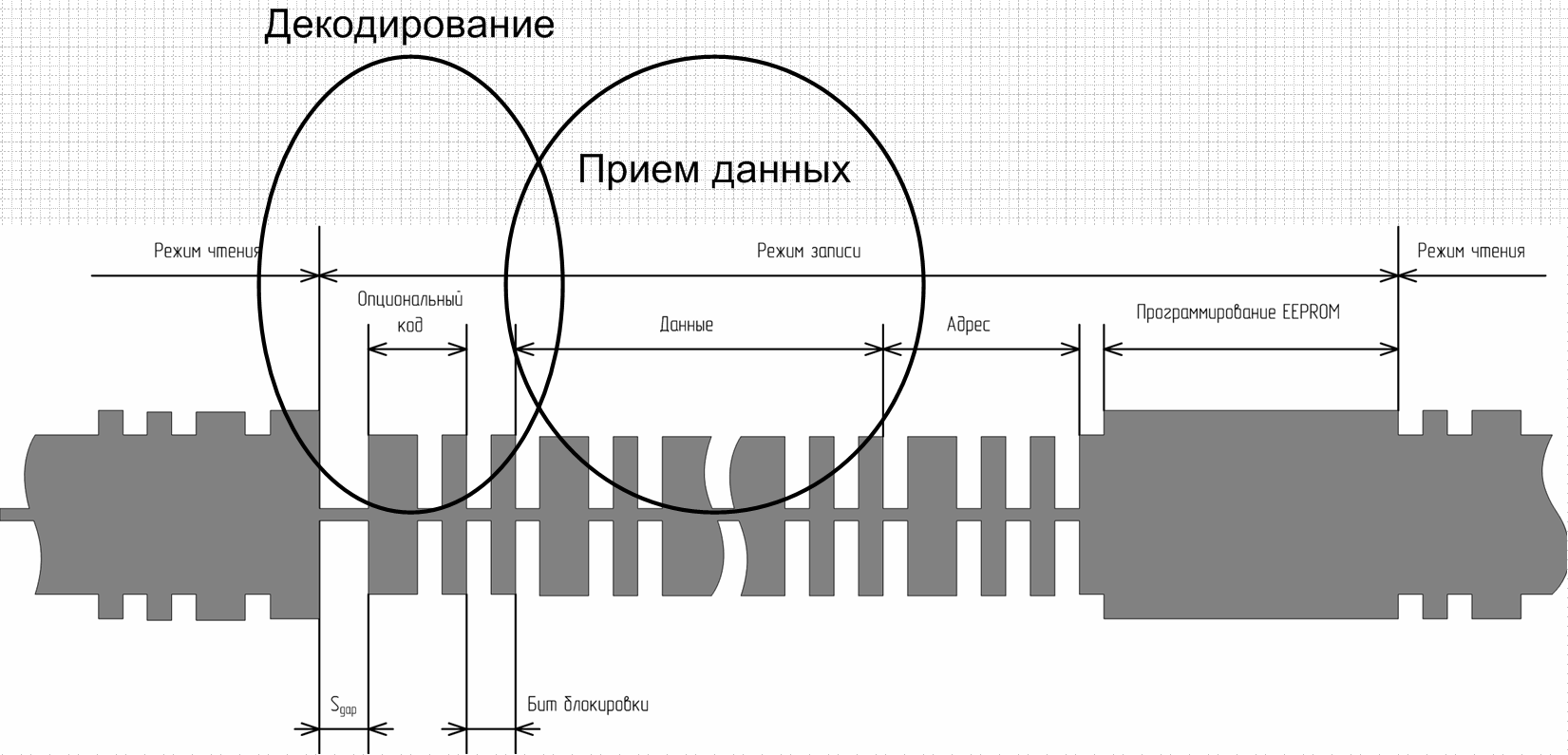

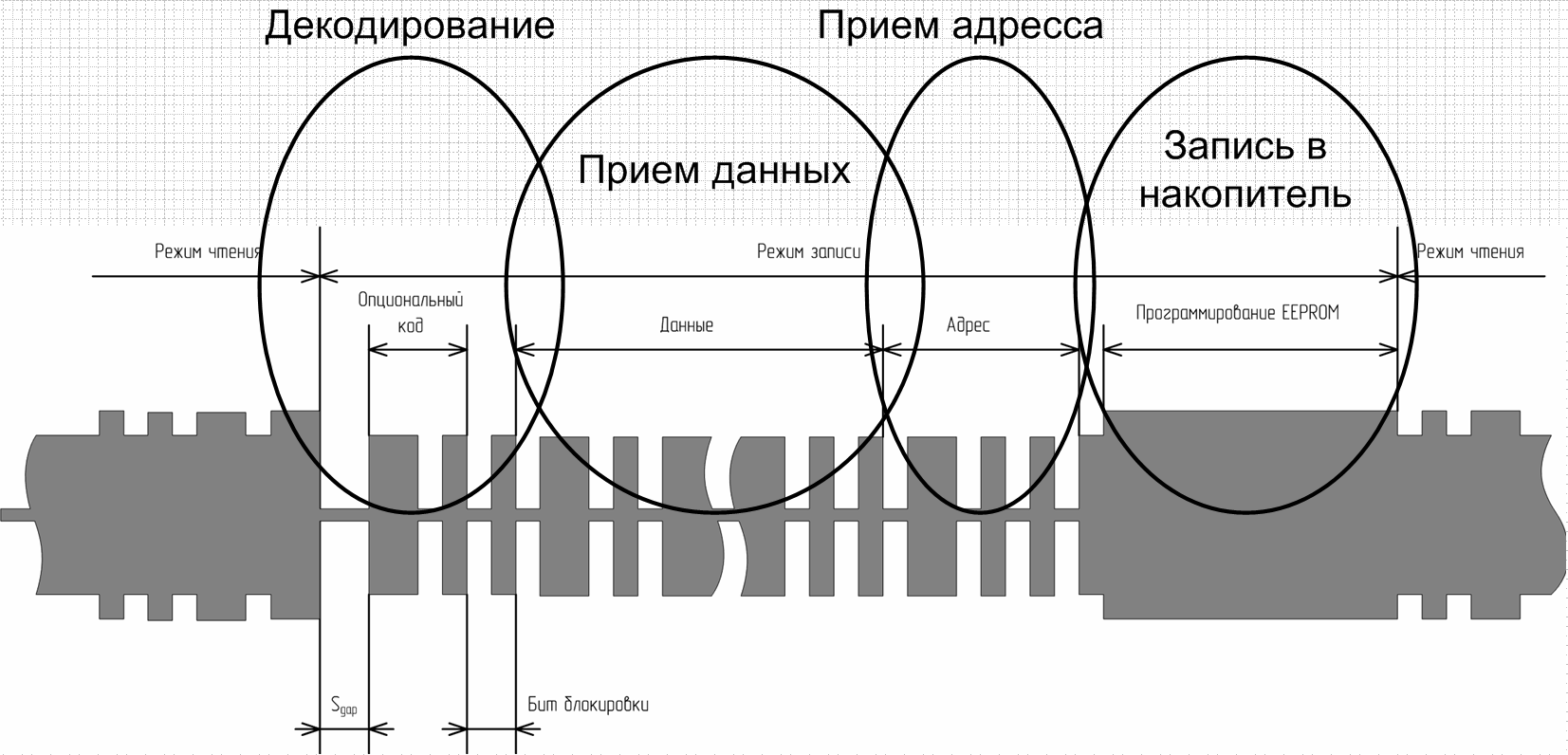

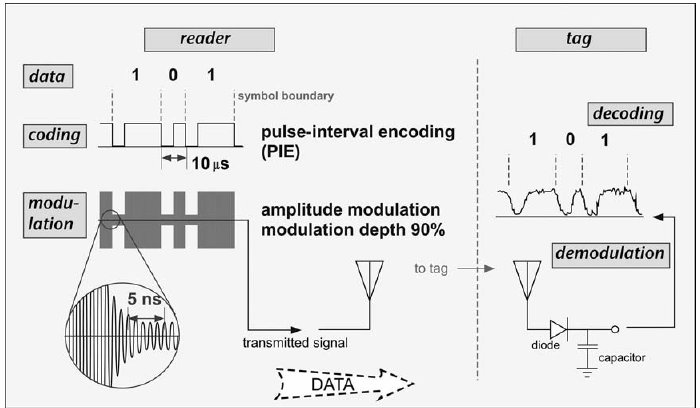

Слайд: Блок обработки данных по протоколу

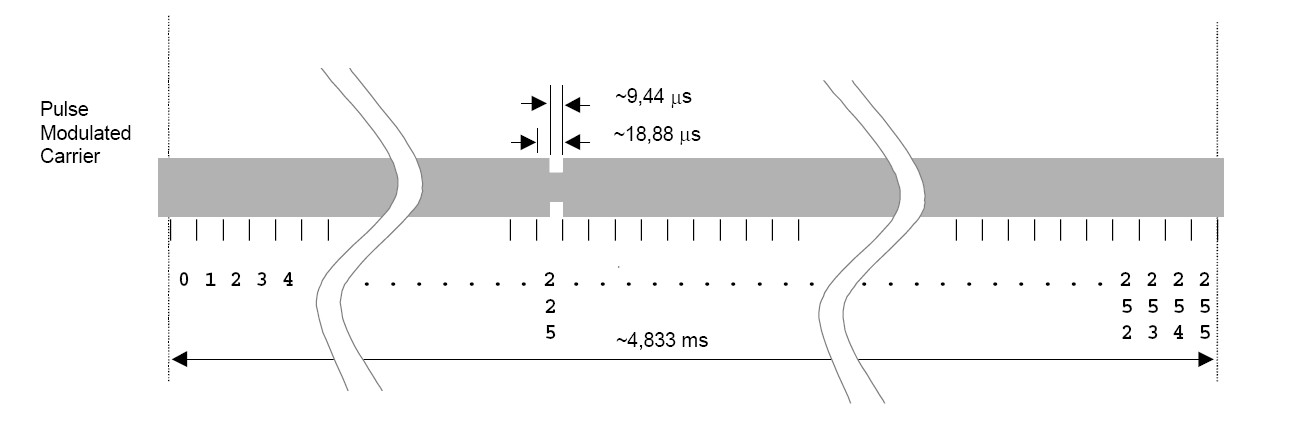

Сигнал на катушке RFID считывателя

architecture beh of fms is

type st_answ_type is (

stanswer_pre,

stanswer_start,

stanswer_data,

stanswer_stop,

stanswer_end

);

signal sta : st_answ_type;

begin -- beh

--=====================================

-- автомат переключения во время ответа

--=====================================

answer_proc: process (clk_answer, rst)

begin -- process answer_proc

if rst = '1' then

sta <= stanswer_pre;

dischargei <= '0';

sta_change <= '0';

elsif clk_answer'event and clk_answer = '0' then

case sta is

when stanswer_pre =>

if st = stanswer then

if count_bit_16 then

sta_change <= not sta_change;

if dischargei = '0' then

sta <= stanswer_start;

else

sta <= stanswer_pre;

--пока включен разряд не выходим из этого состояния

end if;

end if;

end if; |

when stanswer_start =>

if count_bit_8 then

sta <= stanswer_data;

sta_change <= not sta_change;

end if;

when stanswer_data =>

if count_bit_80 then

sta <= stanswer_stop;

sta_change <= not sta_change;

end if;

when stanswer_stop =>

if count_bit_8 then

sta <= stanswer_end;

sta_change <= not sta_change;

end if;

when stanswer_end =>

if count_bit_16 then

dischargei <= '1';

-- если включается разряд то в начало и

sta <= stanswer_pre;

sta_change <= not sta_change;

end if;

when others => sta <= stanswer_pre;

end case;

end if;

end process answer_proc;

--===============================

-- контрольные значения счетчика

--===============================

count_bit_0 <= count_bit = 0;

count_bit_8 <= count_bit = 7;

count_bit_15 <= count_bit = 14;

count_bit_16 <= count_bit = 15;

count_bit_80 <= count_bit = 79;

cmd_BB <= cmd = x"BB";

pwd_EB <= pwd = x"EB";

cmd_cap_write <= cmd(0) = '1';

cmd_cap_read <= cmd(1) = '1';

cmd_write_bc <= cmd(2) = '1';

cmd_readlock <= cmd(3) = '1';

cmd_tst_write <= cmd(4) = '1';

cmd_read_4_8 <= cmd(5) = '1';

cmd_read_0 <= cmd(6) = '1';

cmd_read_1 <= cmd(7) = '1';

end beh; |

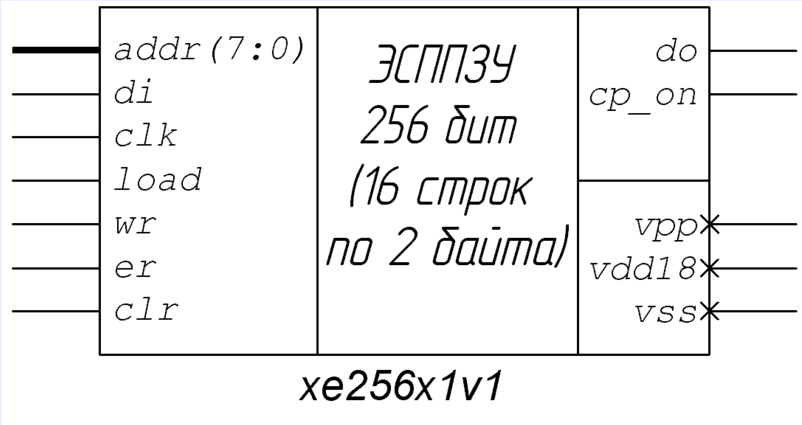

Слайд: Блок чтения из накопителя

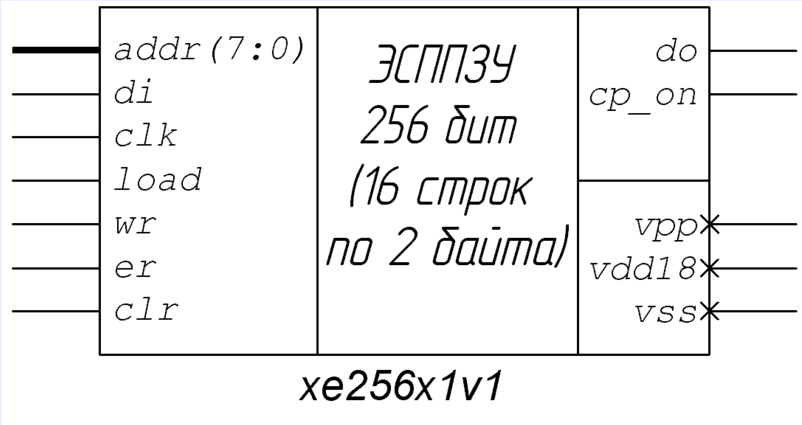

Стандартная конструкция блока хранения информации для RFID

|

- Схематическое отображение блока накопителя

|

library ieee;

-- PACKAGE STATEMENT

use ieee.std_logic_1164.all;

entity xe80x1v2 is

-- GENERIC LIST

generic(

g_mem_init : std_logic_vector(0 to 79) := X"FF962000077900B63467"

);

-- PORT LIST

port(

vpp : inout std_logic;

cp_on : out std_logic;

do : out std_logic;

adr : in std_logic_vector(6 downto 0);

clk : in std_logic;

di : in std_logic;

load : in std_logic;

prog : in std_logic

);

end xe80x1v2; |

Временные диаграммы описывающие протокол записи в накопитель

Пример поведенческой модели накопителя (VHDL)

architecture beh of xe80x1v2 is

signal mem : std_logic_vector(0 to 79) := g_mem_init;

signal invmem : std_logic_vector(79 downto 0) := g_mem_init;

signal addr : std_logic_vector(6 downto 0);

signal write_buffer : std_logic_vector(0 to 79) := (others => '0');

signal rd_nn, wr_n : std_logic;

begin -- beh

vpp <= 'Z' ;

wr_n <= clk and load;

rd_nn <= not ((not prog) and clk and (not load));

cp_on <= not prog;

p1 : process ( wr_n, prog, vpp)

begin -- process p1

if wr_n = '1' then

write_buffer(to_integer(unsigned(adr(6 downto 0)))) <= di;

end if;

if prog = '1' and vpp = 'H' then

mem <= write_buffer after 2 ms;

end if;

end process p1;

do <= mem(to_integer(unsigned(adr))) after 10 ns when (rd_nn = '0') else

'1' after 2 ns ;

inv_gen: for i in 0 to 79 generate

invmem(i) <= mem (i);

end generate inv_gen;

end beh; |

Пример поведенческой модели накопителя (Verilog)

always @(row or col) begin

k=0;

si=0;

sj=0;

i=0;

j=0;

for (i=0; i<14; i=i+1)

for (j=0; j<4; j=j+1)

if (col[i] && row[j])

begin

$display("true decoder data");

k=k+1;

si=i;

sj=j;

end

if (k == 0) #(Tacc) do <= 1'b1;

else if (k == 1) #(Tacc) do <= mem[si][sj];

else do <= 1'bX; |

Слайд: Блок кодирования