Спец курс (Избранные главы VHDL)/Лабораторные работы — различия между версиями

Материал из Wiki

(→Задание 2) |

Vidokq (обсуждение | вклад) (→Общие требования) |

||

| (не показаны 44 промежуточные версии 3 участников) | |||

| Строка 1: | Строка 1: | ||

| − | == | + | {{ИГСАПР_TOC}} |

| + | ==Общие требования == | ||

| + | # Разработать VHDL-описание. | ||

| + | ## Название entity - '''coder''','''decoder'''. | ||

| + | ## Название architecture - '''beh'''. | ||

| + | ## Название портов in - '''D_I, clk, rst'''. | ||

| + | ## Название портов out - '''D_O'''. | ||

| + | ## Внутренние сигналы называть так, чтобы было интуитивно понятно их названия. | ||

| + | # Разработать тестовое окружение для запуска моделирования. | ||

| + | ## На языке SystemC(+) или VHDL. | ||

| + | ## Название entity - '''tb''' (если тестовое окружение на VHDL). | ||

| + | ## Название architecture - '''beh''' (если тестовое окружение на VHDL). | ||

| + | ## Название блока генерации тактового сигнала '''clk_gen (beh)''' | ||

| + | ## Название блока генерации сигнала сброса '''rst_gen (beh)'''. | ||

| + | ## Функция чтения из файла должна быть написана по примеру из [http://gen.lib.rus.ec/book/index.php?md5=EAAEE213147830644F0B955075496847 VHDL. Эффективное использование при проектировании цифровых систем 2006] или [[media:Бибило_П.Н.,_Авдеев_Н.А._VHDL._Эффективное_использование_при_проектировании_цифровых_систем_2006.djvu | Зеркало для скачивания ]] | ||

| + | ## Функция записи в файл должна быть написана по примеру из [http://gen.lib.rus.ec/book/index.php?md5=EAAEE213147830644F0B955075496847 VHDL. Эффективное использование при проектировании цифровых систем 2006] или [[media:Бибило_П.Н.,_Авдеев_Н.А._VHDL._Эффективное_использование_при_проектировании_цифровых_систем_2006.djvu | Зеркало для скачивания ]] | ||

| + | ## Должна быть возможность стыковки tb блока кодирования и декодирования, для верификации. | ||

| + | # Синтезировать полученную схему в LeonardoSpectrum. | ||

| + | # Подготовить лог синтеза, в котором отображаются число элементов или площадь, и максимальное быстродействие схемы. | ||

| + | # Провести моделирование синтезированной схемы. | ||

| − | + | ==Задание 1-1 == | |

| − | + | # Разработать синтезируемое VHDL-описание блока кодирования данных. | |

| − | + | ## Входные порты: D_I, clk, rst. | |

| + | ## Выходные порты: D_O, возможно добавление доп. сигналов обратной связи. | ||

| + | # Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL). | ||

| + | ## Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I. | ||

| + | ## Блок формирования тактового сигнала. | ||

| + | ## Блок формирования сигнала сброса по питанию. | ||

| + | # Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script). | ||

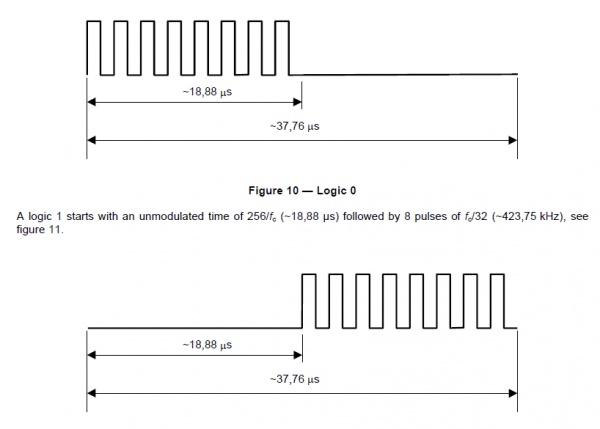

| − | + | * Тип выходной кодировки 1-256 (iso-15693-2) [[Файл:ISO15693-2.pdf]] | |

| − | + | ||

| − | ==Задание 3== | + | [[Файл:1-265_кодировка.jpg|600px]] |

| − | ==Задание | + | |

| − | ==Задание | + | * Частота тактового сигнала 13.56 MHz |

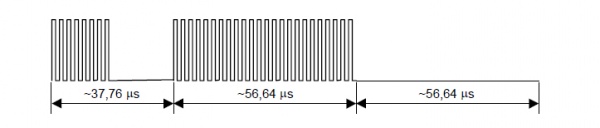

| − | ==Задание 6== | + | * Перед стартом передачи данных посылать SOF |

| − | ==Задание | + | |

| − | ==Задание 8== | + | [[Файл:Sof_1-256_kod.jpg|300px]] |

| − | ==Задание | + | |

| − | ==Задание | + | * После завершения передачи данных EOF |

| + | |||

| + | [[Файл:Eof_1-256.jpg|300px]] | ||

| + | |||

| + | ==Задание 1-2 == | ||

| + | # Разработать синтезируемое VHDL-описание блока декодирования данных. | ||

| + | ## Входные порты: D_I, clk, rst. | ||

| + | ## Выходные порты: D_O, возможно добавление доп. сигналов обратной связи. | ||

| + | # Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных. (Можно на SystemC, можно и на VHDL). | ||

| + | ## Тестовое окружение содержит в себе блок записи принимаемых данных в файл. | ||

| + | ## Блок формирования тактового сигнала. | ||

| + | ## Блок формирования сигнала сброса по питанию. | ||

| + | # Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script). | ||

| + | |||

| + | * Тип входной кодировки 1-256 (iso-15693-2) [[Файл:ISO15693-2.pdf]] | ||

| + | |||

| + | [[Файл:1-265_кодировка.jpg|600px]] | ||

| + | |||

| + | * Частота тактового сигнала 13.56 MHz | ||

| + | * Прием данных начинать после получения SOF | ||

| + | |||

| + | [[Файл:Sof_1-256_kod.jpg|300px| Символ SOF]] | ||

| + | |||

| + | * Прекращать прием после прихода символа EOF | ||

| + | |||

| + | [[Файл:Eof_1-256.jpg|300px| Символ EOF]] | ||

| + | |||

| + | ==Задание 2-1== | ||

| + | |||

| + | # Разработать синтезируемое VHDL-описание блока кодирования данных. | ||

| + | ## Входные порты: D_I, clk, rst. | ||

| + | ## Выходные порты: D_O, возможно добавление доп. сигналов обратной связи. | ||

| + | # Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL). | ||

| + | ## Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I. | ||

| + | ## Блок формирования тактового сигнала. | ||

| + | ## Блок формирования сигнала сброса по питанию. | ||

| + | # Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script). | ||

| + | |||

| + | * Тип выходной кодировки 1-256 (iso-15693-2) [[Файл:ISO15693-2.pdf]] | ||

| + | |||

| + | [[Файл:1-4_кодировка.jpg|600px]] | ||

| + | |||

| + | * Частота тактового сигнала 13.56 MHz | ||

| + | * Перед стартом передачи данных посылать SOF | ||

| + | |||

| + | [[Файл:Sof_1-4_kod.jpg|300px]] | ||

| + | |||

| + | * После завершения передачи данных EOF | ||

| + | |||

| + | [[Файл:Eof_1-256.jpg|300px]] | ||

| + | |||

| + | ==Задание 2-2== | ||

| + | # Разработать синтезируемое VHDL-описание блока декодирования данных. | ||

| + | ## Входные порты: D_I, clk, rst. | ||

| + | ## Выходные порты: D_O, возможно добавление доп. сигналов обратной связи. | ||

| + | # Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных. (Можно на SystemC, можно и на VHDL). | ||

| + | ## Тестовое окружение содержит в себе блок записи принимаемых данных в файл. | ||

| + | ## Блок формирования тактового сигнала. | ||

| + | ## Блок формирования сигнала сброса по питанию. | ||

| + | # Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script). | ||

| + | |||

| + | * Тип выходной кодировки 1-256 (iso-15693-2) [[Файл:ISO15693-2.pdf]] | ||

| + | |||

| + | [[Файл:1-4_кодировка.jpg|600px]] | ||

| + | |||

| + | * Частота тактового сигнала 13.56 MHz | ||

| + | * Перед стартом передачи данных посылать SOF | ||

| + | |||

| + | [[Файл:Sof_1-4_kod.jpg|300px]] | ||

| + | |||

| + | * После завершения передачи данных EOF | ||

| + | |||

| + | [[Файл:Eof_1-256.jpg|300px]] | ||

| + | |||

| + | ==Задание 3-1== | ||

| + | # Разработать синтезируемое VHDL-описание блока кодирования данных. | ||

| + | ## Входные порты: D_I, clk, rst. | ||

| + | ## Выходные порты: D_O, возможно добавление доп. сигналов обратной связи. | ||

| + | # Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL). | ||

| + | ## Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I. | ||

| + | ## Блок формирования тактового сигнала. | ||

| + | ## Блок формирования сигнала сброса по питанию. | ||

| + | # Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script). | ||

| + | |||

| + | * Тип выходной кодировки 1-256 (iso-15693-2) [[Файл:ISO15693-2.pdf]] | ||

| + | |||

| + | [[Файл:Manchester_cod.jpg|600px]] | ||

| + | |||

| + | * Частота тактового сигнала 13.56 MHz | ||

| + | * Перед стартом передачи данных посылать SOF | ||

| + | |||

| + | [[Файл:Sof_manchester_kod.jpg|600px]] | ||

| + | |||

| + | * После завершения передачи данных EOF | ||

| + | |||

| + | [[Файл:Eof_manchester_kod.jpg|600px]] | ||

| + | |||

| + | ==Задание 3-2 == | ||

| + | # Разработать синтезируемое VHDL-описание блока декодирования данных. | ||

| + | ## Входные порты: D_I, clk, rst. | ||

| + | ## Выходные порты: D_O, возможно добавление доп. сигналов обратной связи. | ||

| + | # Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных. (Можно на SystemC, можно и на VHDL). | ||

| + | ## Тестовое окружение содержит в себе блок записи принимаемых данных в файл. | ||

| + | ## Блок формирования тактового сигнала. | ||

| + | ## Блок формирования сигнала сброса по питанию. | ||

| + | # Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script). | ||

| + | |||

| + | * Тип входной кодировки 1-256 (iso-15693-2) [[Файл:ISO15693-2.pdf]] | ||

| + | |||

| + | [[Файл:Manchester_cod.jpg|600px]] | ||

| + | |||

| + | * Частота тактового сигнала 13.56 MHz | ||

| + | * Прием данных начинать после получения SOF | ||

| + | |||

| + | [[Файл:Sof_manchester_kod.jpg|600px| Символ SOF]] | ||

| + | |||

| + | * Прекращать прием после прихода символа EOF | ||

| + | |||

| + | [[Файл:Eof_manchester_kod.jpg|600px| Символ EOF]] | ||

| + | |||

| + | ==Задание 4-1 == | ||

| + | # Разработать синтезируемое VHDL-описание блока кодирования данных. | ||

| + | ## Входные порты: D_I, clk, rst. | ||

| + | ## Выходные порты: D_O, возможно добавление доп. сигналов обратной связи. | ||

| + | # Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL). | ||

| + | ## Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I. | ||

| + | ## Блок формирования тактового сигнала. | ||

| + | ## Блок формирования сигнала сброса по питанию. | ||

| + | ## Выходной порт DATA_O, для выдачи закодированных данных | ||

| + | # Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script). | ||

| + | |||

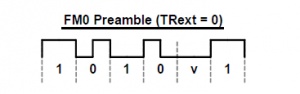

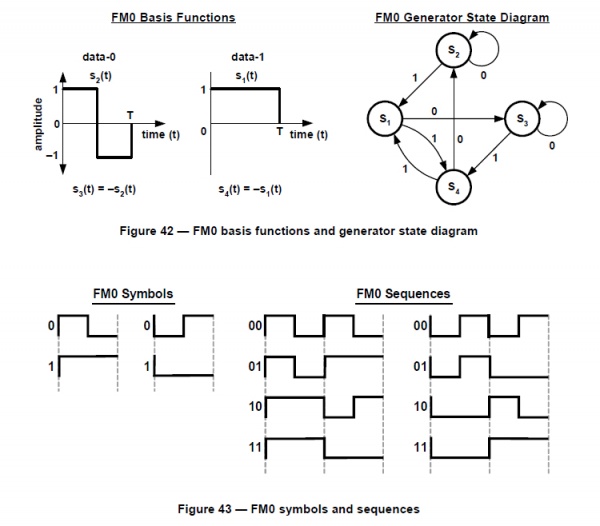

| + | * Тип выходной кодировки FM0 (iso-18000-6) [[Файл:ISO18000-6REV1v62.pdf]] | ||

| + | |||

| + | [[Файл:FM0_кодировка.jpg|500px]] | ||

| + | |||

| + | * Число передаваемых данных задается generic паратмером NUM_SEND_BIT | ||

| + | * Частота тактового сигнала 1.98 MHz | ||

| + | * Частота закодированных данных 640 KHz | ||

| + | * Перед стартом передачи данных посылать SOF | ||

| + | |||

| + | [[Файл:Sof_FM0_kod.jpg|300px]] | ||

| + | |||

| + | * После завершения передачи данных, посылать EOF | ||

| + | |||

| + | [[Файл:Eof_FM0.jpg|300px]] | ||

| + | |||

| + | ==Задание 4-2 == | ||

| + | # Разработать синтезируемое VHDL-описание блока декодирования данных. | ||

| + | ## Входные порты: D_I, clk, rst. | ||

| + | ## Выходные порты: D_O, возможно добавление доп. сигналов обратной связи. | ||

| + | # Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных. (Можно на SystemC, можно и на VHDL). | ||

| + | ## Тестовое окружение содержит в себе блок записи принимаемых данных в файл. | ||

| + | ## Блок формирования тактового сигнала. | ||

| + | ## Блок формирования сигнала сброса по питанию. | ||

| + | # Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script). | ||

| + | |||

| + | * Тип входной кодировки 1-256 (iso-18000-6) [[Файл:ISO18000-6REV1v62.pdf]] | ||

| + | |||

| + | [[Файл:FM0_кодировка.jpg|600px]] | ||

| + | |||

| + | * Число принимаемых данных задается в generic параметре NUM_GET_BIT! | ||

| + | * Частота тактового сигнала 1.92 MHz | ||

| + | * Частота закодированных данных 640 KHz | ||

| + | * Прием данных начинать после получения SOF | ||

| + | |||

| + | [[Файл:Sof_FM0_kod.jpg|300px| Символ SOF]] | ||

| + | |||

| + | * Прекращать прием после прихода символа EOF или после получения заданного числа бит. | ||

| + | |||

| + | [[Файл:Eof_FM0.jpg|300px| Символ EOF]] | ||

| + | |||

| + | ==Задание 5-1 == | ||

| + | # Разработать синтезируемое VHDL-описание блока кодирования данных. | ||

| + | ## Входные порты: D_I, clk, rst. | ||

| + | ## Выходные порты: D_O, возможно добавление доп. сигналов обратной связи. | ||

| + | # Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL). | ||

| + | ## Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I. | ||

| + | ## Блок формирования тактового сигнала. | ||

| + | ## Блок формирования сигнала сброса по питанию. | ||

| + | ## Выходной порт DATA_O, для выдачи закодированных данных | ||

| + | # Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script). | ||

| + | |||

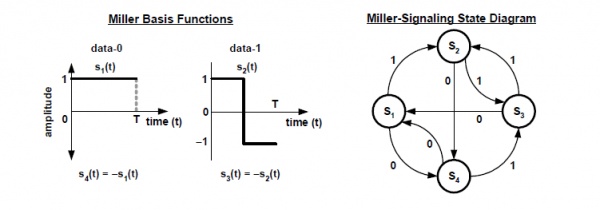

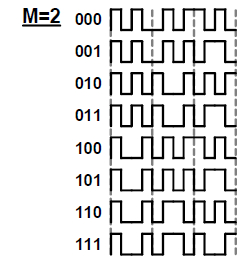

| + | * Тип выходной кодировки код Миллера (iso-18000-6) [[Файл:ISO18000-6REV1v62.pdf]] | ||

| + | |||

| + | [[Файл:Миллер_кодировка.jpg|600px]] | ||

| + | [[Файл:Миллер кодировка состояния.jpg|300px]] | ||

| + | |||

| + | * Число передаваемых данных задается в generic параметре NUM_SEND_BIT ! | ||

| + | * Частота тактового сигнала 1.98 MHz | ||

| + | * Частота закодированных данных 320 KHz (два такта выходной частоты на один бит данных, см. рис.) | ||

| + | * Перед стартом передачи данных посылать SOF | ||

| + | |||

| + | [[Файл:Sof_миллер_kod.jpg|400px]] | ||

| + | |||

| + | * После завершения передачи данных посылать EOF | ||

| + | |||

| + | [[Файл:Eof_миллер.jpg|600px]] | ||

| + | |||

| + | ==Задание 5-2 == | ||

| + | # Разработать синтезируемое VHDL-описание блока декодирования данных. | ||

| + | ## Входные порты: D_I, clk, rst. | ||

| + | ## Выходные порты: D_O, возможно добавление доп. сигналов обратной связи. | ||

| + | # Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных. (Можно на SystemC, можно и на VHDL). | ||

| + | ## Тестовое окружение содержит в себе блок записи принимаемых данных в файл. | ||

| + | ## Блок формирования тактового сигнала. | ||

| + | ## Блок формирования сигнала сброса по питанию. | ||

| + | ## Входной порт DATA_I, для принимаемых от кодера данных | ||

| + | # Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script). | ||

| + | |||

| + | * Тип входной кодировки код Миллера (iso-18000-6) [[Файл:ISO18000-6REV1v62.pdf]] | ||

| + | |||

| + | [[Файл:Миллер_кодировка.jpg|600px]] | ||

| + | [[Файл:Миллер кодировка состояния.jpg|300px]] | ||

| + | |||

| + | * Число принимаемых данных задается в generic параметре NUM_GET_BIT! | ||

| + | * Частота тактового сигнала 1.98 MHz | ||

| + | * Частота закодированных данных 320 KHz (два такта выходной частоты на один бит данных, см. рис.) | ||

| + | * Прием данных начинать после получения SOF | ||

| + | |||

| + | [[Файл:Sof_миллер_kod.jpg|400px| Символ SOF]] | ||

| + | |||

| + | * Прекращать прием после прихода символа EOF или после приема NUM_GET_BIT | ||

| + | |||

| + | [[Файл:Eof_миллер.jpg|400px| Символ EOF]] | ||

| + | |||

| + | ==Задание 6-1== | ||

| + | # Разработать синтезируемое VHDL-описание блока кодирования данных. | ||

| + | ## Входные порты: D_I, clk, rst. | ||

| + | ## Выходные порты: D_O, возможно добавление доп. сигналов обратной связи. | ||

| + | # Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL). | ||

| + | ## Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I. | ||

| + | ## Блок формирования тактового сигнала. | ||

| + | ## Блок формирования сигнала сброса по питанию. | ||

| + | ## Выходной порт DATA_O, для выдачи закодированных данных | ||

| + | # Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script). | ||

| + | |||

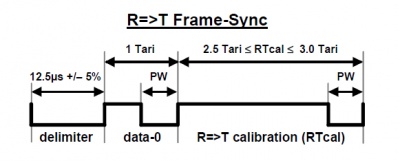

| + | * Тип выходной кодировки iso-18000-6 [[Файл:Input_18000-6_(E)REV1_v62.pdf]] | ||

| + | |||

| + | [[Файл:Input_18000_кодировка.jpg|400px]] | ||

| + | |||

| + | * Число передаваемых данных задается в generic параметре NUM_SEND_BIT ! | ||

| + | * Частота тактового сигнала 8 MHz | ||

| + | * Tari= 6.25us (см. рис.) | ||

| + | * RTcal= (Data-0) + (Data-1)=3 * Tari = 18.75us | ||

| + | * Перед стартом передачи данных посылать SOF | ||

| + | |||

| + | [[Файл:Sof input 18000 kod.jpg|400px]] | ||

| + | |||

| + | * Завершение передачи данных после посылки NUM_SEND_BIT бит данных. | ||

| + | |||

| + | ==Задание 6-2== | ||

| + | |||

| + | # Разработать синтезируемое VHDL-описание блока кодирования данных. | ||

| + | ## Входные порты: D_I, clk, rst. | ||

| + | ## Выходные порты: D_O, возможно добавление доп. сигналов обратной связи. | ||

| + | # Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL). | ||

| + | ## Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I. | ||

| + | ## Блок формирования тактового сигнала. | ||

| + | ## Блок формирования сигнала сброса по питанию. | ||

| + | ## Входной порт DATA_I, для принимаемых от кодера данных | ||

| + | # Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script). | ||

| + | |||

| + | * Тип входной кодировки iso-18000-6 [[Файл:Input_18000-6_(E)REV1_v62.pdf]] | ||

| + | |||

| + | [[Файл:Input_18000_кодировка.jpg|400px]] | ||

| + | |||

| + | * Число принимаемых данных задается в generic параметре NUM_GET_BIT! | ||

| + | * Частота тактового сигнала 1.92 MHz | ||

| + | * Tari= 6.25us (см. рис.) | ||

| + | * RTcal= (Data-0) + (Data-1)=3 * Tari = 18.75us | ||

| + | * Данные декодировать после получения SOF | ||

| + | |||

| + | [[Файл:Sof input 18000 kod.jpg|400px]] | ||

| + | |||

| + | * Полученный символ кодирует 1, если его длинна больше RTcal/2, если меньше, то кодирует логический 0. | ||

| + | * Завершение передачи данных после посылки NUM_SEND_BIT бит данных. | ||

| + | |||

| + | ==Задание 7-1== | ||

| + | # Разработать синтезируемое VHDL-описание блока кодирования данных. | ||

| + | ## Входные порты: D_I, clk, rst. | ||

| + | ## Выходные порты: D_O, возможно добавление доп. сигналов обратной связи. | ||

| + | # Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL). | ||

| + | ## Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I. | ||

| + | ## Блок формирования тактового сигнала. | ||

| + | ## Блок формирования сигнала сброса по питанию. | ||

| + | ## Выходной порт DATA_O, для выдачи закодированных данных | ||

| + | # Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script). | ||

| + | |||

| + | * Тип выходной кодировки ATA-5575 [[Файл:Doc9167.pdf]] | ||

| + | |||

| + | [[Файл:Wrie_mode_raduga1.jpg|300px]] | ||

| + | |||

| + | * Число передаваемых данных задается в generic параметре NUM_SEND_BIT ! | ||

| + | * Частота тактового сигнала 125 КHz | ||

| + | * Для кодирования данных смотри таблицу | ||

| + | * Старт передачи данных - первая пауза. | ||

| + | |||

| + | [[Файл:Wrie_mode_raduga1_table.jpg|600px]] | ||

| + | |||

| + | * Завершение передачи данных после посылки NUM_SEND_BIT бит данных. | ||

| + | |||

| + | ==Задание 7-2== | ||

| + | # Разработать синтезируемое VHDL-описание блока декодирования данных. | ||

| + | ## Входные порты: D_I, clk, rst. | ||

| + | ## Выходные порты: D_O, возможно добавление доп. сигналов обратной связи. | ||

| + | # Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL). | ||

| + | ## Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I. | ||

| + | ## Блок формирования тактового сигнала. | ||

| + | ## Блок формирования сигнала сброса по питанию. | ||

| + | ## Выходной порт DATA_O, для выдачи закодированных данных | ||

| + | # Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script). | ||

| + | |||

| + | * Тип входной кодировки ATA-5575 [[Файл:Doc9167.pdf]] | ||

| + | |||

| + | [[Файл:Wrie_mode_raduga1.jpg|300px]] | ||

| + | |||

| + | * Число передаваемых данных задается в generic параметре NUM_SEND_BIT ! | ||

| + | * Частота тактового сигнала 125 КHz | ||

| + | * Для декодирования данных смотри таблицу | ||

| + | * Старт приема данных - первая пауза D_I равен 0. | ||

| + | |||

| + | [[Файл:Wrie_mode_raduga1_table.jpg|600px]] | ||

| + | |||

| + | * Завершение приема данных после получения NUM_SEND_BIT бит данных. | ||

Текущая версия на 17:36, 16 декабря 2013

Лекции ИГСАПР

Лекции

Практические

- Тест 1 по RFID системам

- Тест 2 по основам языка VHDL (начальный уровень)

- Тест 3 по языку VHDL (экспертный уровень)

- Тест 4 Среда моделирования

- Тест 5 Верификация VHDL-описания

- Тест 6 Основы языка SystemC

Лабораторные

- Лабораторные работы

Табель

Доп. материалы

Содержание |

Общие требования

- Разработать VHDL-описание.

- Название entity - coder,decoder.

- Название architecture - beh.

- Название портов in - D_I, clk, rst.

- Название портов out - D_O.

- Внутренние сигналы называть так, чтобы было интуитивно понятно их названия.

- Разработать тестовое окружение для запуска моделирования.

- На языке SystemC(+) или VHDL.

- Название entity - tb (если тестовое окружение на VHDL).

- Название architecture - beh (если тестовое окружение на VHDL).

- Название блока генерации тактового сигнала clk_gen (beh)

- Название блока генерации сигнала сброса rst_gen (beh).

- Функция чтения из файла должна быть написана по примеру из VHDL. Эффективное использование при проектировании цифровых систем 2006 или Зеркало для скачивания

- Функция записи в файл должна быть написана по примеру из VHDL. Эффективное использование при проектировании цифровых систем 2006 или Зеркало для скачивания

- Должна быть возможность стыковки tb блока кодирования и декодирования, для верификации.

- Синтезировать полученную схему в LeonardoSpectrum.

- Подготовить лог синтеза, в котором отображаются число элементов или площадь, и максимальное быстродействие схемы.

- Провести моделирование синтезированной схемы.

Задание 1-1

- Разработать синтезируемое VHDL-описание блока кодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

- Тип выходной кодировки 1-256 (iso-15693-2) Файл:ISO15693-2.pdf

- Частота тактового сигнала 13.56 MHz

- Перед стартом передачи данных посылать SOF

- После завершения передачи данных EOF

Задание 1-2

- Разработать синтезируемое VHDL-описание блока декодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных. (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок записи принимаемых данных в файл.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

- Тип входной кодировки 1-256 (iso-15693-2) Файл:ISO15693-2.pdf

- Частота тактового сигнала 13.56 MHz

- Прием данных начинать после получения SOF

- Прекращать прием после прихода символа EOF

Задание 2-1

- Разработать синтезируемое VHDL-описание блока кодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

- Тип выходной кодировки 1-256 (iso-15693-2) Файл:ISO15693-2.pdf

- Частота тактового сигнала 13.56 MHz

- Перед стартом передачи данных посылать SOF

- После завершения передачи данных EOF

Задание 2-2

- Разработать синтезируемое VHDL-описание блока декодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных. (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок записи принимаемых данных в файл.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

- Тип выходной кодировки 1-256 (iso-15693-2) Файл:ISO15693-2.pdf

- Частота тактового сигнала 13.56 MHz

- Перед стартом передачи данных посылать SOF

- После завершения передачи данных EOF

Задание 3-1

- Разработать синтезируемое VHDL-описание блока кодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

- Тип выходной кодировки 1-256 (iso-15693-2) Файл:ISO15693-2.pdf

- Частота тактового сигнала 13.56 MHz

- Перед стартом передачи данных посылать SOF

- После завершения передачи данных EOF

Задание 3-2

- Разработать синтезируемое VHDL-описание блока декодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных. (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок записи принимаемых данных в файл.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

- Тип входной кодировки 1-256 (iso-15693-2) Файл:ISO15693-2.pdf

- Частота тактового сигнала 13.56 MHz

- Прием данных начинать после получения SOF

- Прекращать прием после прихода символа EOF

Задание 4-1

- Разработать синтезируемое VHDL-описание блока кодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Выходной порт DATA_O, для выдачи закодированных данных

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

- Тип выходной кодировки FM0 (iso-18000-6) Файл:ISO18000-6REV1v62.pdf

- Число передаваемых данных задается generic паратмером NUM_SEND_BIT

- Частота тактового сигнала 1.98 MHz

- Частота закодированных данных 640 KHz

- Перед стартом передачи данных посылать SOF

- После завершения передачи данных, посылать EOF

Задание 4-2

- Разработать синтезируемое VHDL-описание блока декодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных. (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок записи принимаемых данных в файл.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

- Тип входной кодировки 1-256 (iso-18000-6) Файл:ISO18000-6REV1v62.pdf

- Число принимаемых данных задается в generic параметре NUM_GET_BIT!

- Частота тактового сигнала 1.92 MHz

- Частота закодированных данных 640 KHz

- Прием данных начинать после получения SOF

- Прекращать прием после прихода символа EOF или после получения заданного числа бит.

Задание 5-1

- Разработать синтезируемое VHDL-описание блока кодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Выходной порт DATA_O, для выдачи закодированных данных

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

- Тип выходной кодировки код Миллера (iso-18000-6) Файл:ISO18000-6REV1v62.pdf

- Число передаваемых данных задается в generic параметре NUM_SEND_BIT !

- Частота тактового сигнала 1.98 MHz

- Частота закодированных данных 320 KHz (два такта выходной частоты на один бит данных, см. рис.)

- Перед стартом передачи данных посылать SOF

- После завершения передачи данных посылать EOF

Задание 5-2

- Разработать синтезируемое VHDL-описание блока декодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных. (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок записи принимаемых данных в файл.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Входной порт DATA_I, для принимаемых от кодера данных

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

- Тип входной кодировки код Миллера (iso-18000-6) Файл:ISO18000-6REV1v62.pdf

- Число принимаемых данных задается в generic параметре NUM_GET_BIT!

- Частота тактового сигнала 1.98 MHz

- Частота закодированных данных 320 KHz (два такта выходной частоты на один бит данных, см. рис.)

- Прием данных начинать после получения SOF

- Прекращать прием после прихода символа EOF или после приема NUM_GET_BIT

Задание 6-1

- Разработать синтезируемое VHDL-описание блока кодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Выходной порт DATA_O, для выдачи закодированных данных

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

- Тип выходной кодировки iso-18000-6 Файл:Input 18000-6 (E)REV1 v62.pdf

- Число передаваемых данных задается в generic параметре NUM_SEND_BIT !

- Частота тактового сигнала 8 MHz

- Tari= 6.25us (см. рис.)

- RTcal= (Data-0) + (Data-1)=3 * Tari = 18.75us

- Перед стартом передачи данных посылать SOF

- Завершение передачи данных после посылки NUM_SEND_BIT бит данных.

Задание 6-2

- Разработать синтезируемое VHDL-описание блока кодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Входной порт DATA_I, для принимаемых от кодера данных

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

- Тип входной кодировки iso-18000-6 Файл:Input 18000-6 (E)REV1 v62.pdf

- Число принимаемых данных задается в generic параметре NUM_GET_BIT!

- Частота тактового сигнала 1.92 MHz

- Tari= 6.25us (см. рис.)

- RTcal= (Data-0) + (Data-1)=3 * Tari = 18.75us

- Данные декодировать после получения SOF

- Полученный символ кодирует 1, если его длинна больше RTcal/2, если меньше, то кодирует логический 0.

- Завершение передачи данных после посылки NUM_SEND_BIT бит данных.

Задание 7-1

- Разработать синтезируемое VHDL-описание блока кодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Выходной порт DATA_O, для выдачи закодированных данных

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

- Тип выходной кодировки ATA-5575 Файл:Doc9167.pdf

- Число передаваемых данных задается в generic параметре NUM_SEND_BIT !

- Частота тактового сигнала 125 КHz

- Для кодирования данных смотри таблицу

- Старт передачи данных - первая пауза.

- Завершение передачи данных после посылки NUM_SEND_BIT бит данных.

Задание 7-2

- Разработать синтезируемое VHDL-описание блока декодирования данных.

- Входные порты: D_I, clk, rst.

- Выходные порты: D_O, возможно добавление доп. сигналов обратной связи.

- Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL).

- Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I.

- Блок формирования тактового сигнала.

- Блок формирования сигнала сброса по питанию.

- Выходной порт DATA_O, для выдачи закодированных данных

- Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script).

- Тип входной кодировки ATA-5575 Файл:Doc9167.pdf

- Число передаваемых данных задается в generic параметре NUM_SEND_BIT !

- Частота тактового сигнала 125 КHz

- Для декодирования данных смотри таблицу

- Старт приема данных - первая пауза D_I равен 0.

- Завершение приема данных после получения NUM_SEND_BIT бит данных.