Спец курс (Избранные главы VHDL)/Вспомним VHDL — различия между версиями

Vidokq (обсуждение | вклад) (→VHDL-основные конструкции) |

Vidokq (обсуждение | вклад) (→Слайд:Работа с редактором EMACS) |

||

| (не показаны 40 промежуточных версий 2 участников) | |||

| Строка 1: | Строка 1: | ||

| + | {{ИГСАПР_TOC}} | ||

<slideshow style="custis" headingmark="Слайд:" incmark=":step" scaled="true" > | <slideshow style="custis" headingmark="Слайд:" incmark=":step" scaled="true" > | ||

;title: '''Вспомнить все...''' | ;title: '''Вспомнить все...''' | ||

| Строка 24: | Строка 25: | ||

** {{Зел|'''CDL, DDL, ISPS, CONLAN, HILO'''}} | ** {{Зел|'''CDL, DDL, ISPS, CONLAN, HILO'''}} | ||

| − | ==VHDL | + | ==VHDL ссылки и литература== |

| − | + | ||

| + | {{Кр|<big>'''Все примеры взяты с сайта БГУИР'''</big>}} | ||

| − | === Entity === | + | [http://www.bsuir.by/vhdl/ Сайт БГУИР с материалами по VHDL] |

| + | *[[File:Шпаргалка по VHDL.pdf]] | ||

| + | *[[File:Шпаргалка по VHDL(типы данных).pdf]] | ||

| + | [[Файл: Заставка_для_БГУИР.jpg]] | ||

| + | |||

| + | ===Слайд: Entity === | ||

<source lang="vhdl"> | <source lang="vhdl"> | ||

library ieee; | library ieee; | ||

| Строка 41: | Строка 47: | ||

end xc; | end xc; | ||

</source> | </source> | ||

| − | |||

| − | |||

<div class="tleft" style="clear:none">[[Файл:Пример_entity.jpg|600px|Entity]]</div> | <div class="tleft" style="clear:none">[[Файл:Пример_entity.jpg|600px|Entity]]</div> | ||

| − | |||

| − | |||

| − | |||

<br clear="all" /> | <br clear="all" /> | ||

| − | ===Architecture=== | + | ===Слайд: Architecture=== |

<source lang="vhdl">architecture beh of trig is | <source lang="vhdl">architecture beh of trig is | ||

begin -- beh | begin -- beh | ||

end beh;</source> | end beh;</source> | ||

| − | |||

| − | |||

<div class="tleft" style="clear:none">[[Файл:Пример_architecture.jpg|600px|architecture]]</div> | <div class="tleft" style="clear:none">[[Файл:Пример_architecture.jpg|600px|architecture]]</div> | ||

| − | |||

| − | |||

| − | |||

| − | |||

<br clear="all" /> | <br clear="all" /> | ||

| − | ===Process=== | + | ===Слайд: Process=== |

| − | <source lang="vhdl"> | + | |

| + | {| width=800px | ||

| + | |<source lang="vhdl"> | ||

| + | trig_process: process (clk, rst) | ||

begin -- process trig_process | begin -- process trig_process | ||

| − | if rst = '0' then | + | if rst = '0' then -- asynchronous reset (active low) |

data_out <= '0'; | data_out <= '0'; | ||

elsif clk'event and clk = '1' then -- rising clock edge | elsif clk'event and clk = '1' then -- rising clock edge | ||

data_out <= data_in; | data_out <= data_in; | ||

end if; | end if; | ||

| − | end process trig_process;</source> | + | end process trig_process; |

| + | </source> | ||

| − | |||

| − | |||

| − | |||

| − | === When Else === | + | {{Info| Далее подробнее}} |

| + | |} | ||

| + | |||

| + | ===Слайд: When Else === | ||

<source lang="vhdl"> | <source lang="vhdl"> | ||

t1 <= not t1 when clk'event and clk = '1' else | t1 <= not t1 when clk'event and clk = '1' else | ||

t1; | t1; | ||

</source> | </source> | ||

| + | {{SideBar40|Данная запись является компактным описанием счетного триггера, но она не соответствует стандарту синтезируемого подмножества. Поэтому не все системы синтеза её поддерживают. Например, {{Зел|'''Leonardo Spectrum'''}} синтезирует данную конструкцию, а в ранних версиях {{Кр|'''Synopsys`а'''}} эта запись не поддерживалась.}} | ||

| + | <br clear="all" /> | ||

| − | === | + | === Примеры кода на VHDL === |

| + | '''Логическое ИЛИ''' | ||

| − | + | <slides split="-----" width="200"> | |

| + | <source lang="vhdl"> | ||

| + | entity and2 is -- декларация имени объекта проекта | ||

| + | port (x1,x2: in BIT; -- декларация входных портов | ||

| + | y: out BIT); -- декларация выходного порта | ||

| + | end and2; | ||

| − | < | + | architecture functional of and2 is -- декларация архитектуры |

| − | < | + | begin |

| − | < | + | y <= x1 and x2; -- описание функции объекта |

| − | </ | + | end functional;</source> |

| + | |||

| + | ----- | ||

| + | '''Схема посложнее''' | ||

| + | <source lang="vhdl"> | ||

| + | entity add1 is | ||

| + | port (b1,b2 : in BIT; | ||

| + | c1,s1 : out BIT); | ||

| + | end add1; | ||

| + | |||

| + | architecture struct_1 of add1 is | ||

| + | begin | ||

| + | s1 <= ((b1 and (not b2)) or ((not b1) and b2)); | ||

| + | c1 <= b1 and b2; | ||

| + | end struct_1;</source> | ||

| + | |||

| + | ----- | ||

| + | '''Описание несколько схем в одном теле архитектуры''' | ||

| + | <source lang="vhdl"> | ||

| + | entity add2 is | ||

| + | port (c1, a1, a2 : in BIT; | ||

| + | c2, s2 : out BIT); | ||

| + | end add2; | ||

| + | |||

| + | architecture struct_1 of add2 is | ||

| + | begin | ||

| + | s2 <= ((not c1) and (not a1) and a2) or | ||

| + | ((not c1) and a1 and (not a2)) or | ||

| + | ( c1 and (not a1)and (not a2) ) or | ||

| + | (a1 and a2 and c1); | ||

| + | c2 <= (a1 and c1) or (a2 and c1) or (a1 and a2); | ||

| + | end struct_1; | ||

| + | </source> | ||

| + | |||

| + | ----- | ||

| + | '''Использование компонент для выполнения повторяющихся частей кода''' | ||

| + | <source lang="vhdl">entity mult_2 is | ||

| + | port (s1,s0,r1,r0 : in BIT; | ||

| + | t3,t2,t1,t0 : out BIT); | ||

| + | end mult_2; | ||

| + | |||

| + | architecture structure of mult_2 is | ||

| + | component add1 | ||

| + | port (b1,b2: in BIT; | ||

| + | c1,s1: out BIT); | ||

| + | end component; | ||

| + | |||

| + | signal p1,p2,p3,p4 : BIT; | ||

| + | begin | ||

| + | t0 <= r0 and s0; -- элемент el_1 | ||

| + | p2 <= r0 and s1; -- элемент el_3 | ||

| + | p1 <= r1 and s0; -- элемент el_2 | ||

| + | p4 <= r1 and s1; -- элемент el_4 | ||

| + | circ1: add1 port map (p1, p2, p3,t1); | ||

| + | circ2: add1 port map (p3,p4,t3,t2); | ||

| + | end structure; | ||

| + | </source> | ||

| + | |||

| + | ----- | ||

| + | '''Подключение различных компонент''' | ||

| + | <source lang="vhdl"> | ||

| + | entity adder_2 is | ||

| + | port (a1, b1, a2,b2 : in BIT; | ||

| + | c2,s2,s1 : out BIT); | ||

| + | end adder_2; | ||

| + | |||

| + | architecture structure of adder_2 is | ||

| + | component add1 | ||

| + | port (b1,b2: in BIT; | ||

| + | c1,s1: out BIT); | ||

| + | end component; | ||

| + | |||

| + | component add2 | ||

| + | port(c1, a1,a2:in BIT; | ||

| + | c2,s2:out BIT); | ||

| + | end component; | ||

| + | signal c1: BIT; | ||

| + | begin | ||

| + | |||

| + | circ1: add1 port map (b1,b2, c1,s1); | ||

| + | circ2: add2 port map (c1,a1,a2,c2,s2); | ||

| + | end structure; | ||

| + | </source> | ||

| + | |||

| + | ----- | ||

| + | '''Иерархия в структуре проета''' | ||

| + | <source lang="vhdl">entity vlsi_1 is | ||

| + | port (a2, a1, b2,b1,x:in BIT; | ||

| + | d4,d3,d2,d1: out BIT); | ||

| + | end vlsi_1; | ||

| + | architecture structure of vlsi_1 is | ||

| + | |||

| + | component adder_2 -- декларация компонента | ||

| + | port (a1,b1,a2,b2: in BIT; | ||

| + | c2,s2,s1: out BIT); | ||

| + | end component; | ||

| + | component mult_2 -- декларация компонента | ||

| + | port(s1,s0, r1,r0: in BIT; | ||

| + | t3,t2,t1,t0: out BIT); | ||

| + | end component; | ||

| + | component dd -- декларация компонента | ||

| + | port (x1,x2,x3,x4,x5,x6 : in BIT; | ||

| + | y1,y2,y3 : out BIT); | ||

| + | end component; | ||

| + | component yy -- декларация компонента | ||

| + | port(a2,a1,b2,b1,x : in BIT; | ||

| + | f6,f5,f4,f3,f2,f1 : out bit); | ||

| + | end component; | ||

| + | signal f1,f2,f3,f4,f5,f6,t4,t3,t2,t1,c2,s2,s1: BIT; -- декларация внутренних сигналов | ||

| + | |||

| + | begin | ||

| + | circ1: yy port map (a2,a1, b2,b1, x, f6,f5,f4,f3,f2,f1); | ||

| + | circ2: mult_2 port map (f2,f1, b2,b1, d4,t3,t2,t1); | ||

| + | circ3: adder_2 port map (f4,f3, f6,f5,c2,s2,s1); | ||

| + | circ4: dd port map (s1,t1,s2,t2,c2,t3, d1,d2,d3); | ||

| + | end structure; | ||

| + | </source> | ||

| + | |||

| + | ----- | ||

| + | '''Схема без иерархии''' | ||

| + | <source lang="vhdl">entity YY is | ||

| + | port (a2,a1,b2,b1, x : in BIT; | ||

| + | f6,f5,f4,f3,f2,f1 : out BIT); | ||

| + | end YY; | ||

| + | architecture struct_1 of YY is | ||

| + | begin | ||

| + | f1<= x and a1; | ||

| + | f2<= x and a2; | ||

| + | f3<= not x and a1; | ||

| + | f4 <= not x and a2; | ||

| + | f5 <= not x and b1; | ||

| + | f6 <= not x and b2; | ||

| + | end struct_1; | ||

| + | </source> | ||

| + | ----- | ||

| + | '''Паралельные операторы''' | ||

| + | <source lang="vhdl">entity dd is | ||

| + | port (x1,x2,x3,x4,x5,x6 : in BIT; | ||

| + | y1, y2, y3 : out BIT); | ||

| + | end dd; | ||

| + | architecture struct_1 of dd is | ||

| + | begin | ||

| + | y1<= x1 or x2; | ||

| + | y2<= x3 or x4; | ||

| + | y3<= x5 or x6; | ||

| + | end struct_1;</source> | ||

| + | ----- | ||

| + | '''Последовательные операторы''' | ||

| + | <source lang="vhdl">entity vlsi_1 is | ||

| + | port (a, b : in integer range 0 to 3; | ||

| + | x : in BIT; | ||

| + | D : out integer range 0 to 15); | ||

| + | end vlsi_1; | ||

| + | |||

| + | architecture functional of vlsi_1 is | ||

| + | signal e: integer range 0 to 15; | ||

| + | begin | ||

| + | p0: process(a, b, x) | ||

| + | begin | ||

| + | if (x='0') then | ||

| + | e <= a + b; | ||

| + | elsif (x = '1') then | ||

| + | e <= a * b ; | ||

| + | end if; | ||

| + | end process; | ||

| + | D <= e; | ||

| + | end functional;</source> | ||

| + | |||

| + | ----- | ||

| + | '''Использование функций''' | ||

| + | <source lang="vhdl">package multiplexer is | ||

| + | procedure MX( | ||

| + | signal SEL : in bit; | ||

| + | signal x0 : in bit; | ||

| + | signal x1 : in bit; | ||

| + | signal F : out bit); | ||

| + | end multiplexer; | ||

| + | package body multiplexer is | ||

| + | procedure MX( | ||

| + | signal SEL : in bit; | ||

| + | signal x0 : in bit; | ||

| + | signal x1 : in bit; | ||

| + | signal F : out bit) is | ||

| + | begin | ||

| + | case SEL is | ||

| + | when '0' => F <= x0; | ||

| + | when others => F <= x1; | ||

| + | end case; | ||

| + | end MX; | ||

| + | end multiplexer; | ||

| + | </source> | ||

| + | ----- | ||

| + | '''Несколько архитектур''' | ||

| + | <source lang="vhdl">entity ANDOR is | ||

| + | port (x1, x2, x3 : in bit; | ||

| + | f : out bit); | ||

| + | end ANDOR; | ||

| + | architecture RTL1 of ANDOR is | ||

| + | begin | ||

| + | f <= (x1 and x2) or x3; | ||

| + | end RTL1; | ||

| + | architecture RTL2 of ANDOR is | ||

| + | signal w : bit; | ||

| + | begin | ||

| + | w <= x1 and x2; | ||

| + | p1 : process (w, x3) | ||

| + | begin | ||

| + | f <= w or x3; | ||

| + | end process p1; | ||

| + | end RTL2;</source> | ||

| + | |||

| + | ----- | ||

| + | '''Понятие сигнала''' | ||

| + | <source lang="vhdl">entity ANDOR is | ||

| + | port( x1, x2, x3 : in bit; | ||

| + | f : out bit); | ||

| + | end ANDOR; | ||

| + | architecture example of ANDOR is | ||

| + | signal w : bit; | ||

| + | begin | ||

| + | p0 : w <= x1 and x2 after 10 ns; | ||

| + | p1 : process (w, x3) | ||

| + | begin | ||

| + | f <= w or x3 after 20 ns; | ||

| + | end process p1; | ||

| + | end example;</source> | ||

| + | |||

| + | ----- | ||

| + | ''' Дельта-задержка ''' | ||

| + | |||

| + | <source lang="vhdl">entity ANDOR is | ||

| + | port( x1, x2, x3 : in bit; | ||

| + | f : out bit); | ||

| + | end ANDOR; | ||

| + | architecture DELTA of ANDOR is | ||

| + | signal w:bit; | ||

| + | begin | ||

| + | p0: w<= x1 and x2; -- нет слова after | ||

| + | p1: process(w, x3) | ||

| + | begin | ||

| + | f<=w or x3; -- нет слова after | ||

| + | end process p1; | ||

| + | end DELTA;</source> | ||

| + | |||

| + | ----- | ||

| + | '''Последовательные операторы''' | ||

| + | <source lang="vhdl"> entity VAR is | ||

| + | end VAR; | ||

| + | architecture functional of VAR is | ||

| + | signal A, B, J : bit_vector(1 downto 0); | ||

| + | signal E, F, G : bit; | ||

| + | begin | ||

| + | p0 : process (A, B, E, F, G, J) | ||

| + | variable C, D, H, Y : bit_vector(1 downto 0); | ||

| + | variable W, Q : bit_vector(3 downto 0); | ||

| + | variable Z : bit_vector(0 to 7); | ||

| + | variable X : bit; | ||

| + | variable DATA : bit_vector(31 downto 0); | ||

| + | begin | ||

| + | C := "11"; | ||

| + | X := E and F; | ||

| + | Y := H nand J; | ||

| + | Z(0 to 3) := C & D; -- конкатенация | ||

| + | Z(4 to 7) := (not A) & (A nor B); -- конкатенация | ||

| + | D := ('0', '0'); -- агрегат | ||

| + | W := (2 downto 1 => G, 3 => '1', others => '0'); -- агрегат | ||

| + | DATA := (others => '1'); -- агрегат | ||

| + | end process; | ||

| + | end functional; | ||

| + | </source> | ||

| + | ----- | ||

| + | '''Тригер и логика''' | ||

| + | <source lang="vhdl">entity IFSTMT is | ||

| + | port ( | ||

| + | RSTn, CLK, EN, PL : in bit; | ||

| + | DATA : in integer range 0 to 31; | ||

| + | COUNT : out integer range 0 to 31); | ||

| + | end IFSTMT; | ||

| + | architecture RTL of IFSTMT is | ||

| + | signal COUNT_VALUE : integer range 0 to 31; | ||

| + | begin | ||

| + | p0 : process (RSTn, CLK) | ||

| + | begin | ||

| + | if (RSTn = '0') then | ||

| + | COUNT_VALUE <= 0; | ||

| + | elsif (CLK'event and CLK = '1') then | ||

| + | if (PL = '1') then | ||

| + | COUNT_VALUE <= DATA; | ||

| + | elsif (EN = '1') then | ||

| + | if (COUNT_VALUE = 31) then | ||

| + | COUNT_VALUE <= 0; | ||

| + | else | ||

| + | COUNT_VALUE <= COUNT_VALUE + 1; | ||

| + | end if; | ||

| + | end if; | ||

| + | end if; | ||

| + | end process; | ||

| + | COUNT <= COUNT_VALUE; | ||

| + | end RTL; | ||

| + | </source> | ||

| + | ----- | ||

| + | ''' Параллельные операторы''' | ||

| + | |||

| + | <source lang="vhdl"> entity call_parallel is | ||

| + | port ( | ||

| + | data_inp : in bit_vector(5 downto 0); | ||

| + | data_out : out bit_vector(1 downto 0)); | ||

| + | end call_parallel; | ||

| + | architecture RTL of call_parallel is | ||

| + | procedure N_XOR ( | ||

| + | signal x1, x2, x3 : in bit; | ||

| + | signal f : out bit) is | ||

| + | begin | ||

| + | f <= x1 xor x2 xor x3; | ||

| + | end N_XOR; | ||

| + | begin | ||

| + | N_XOR (x1 => data_inp(5), x2 => data_inp(4), x3 => data_inp(3), f => data_out(1)); | ||

| + | p0 : N_XOR (data_inp(2), data_inp(1), data_inp(0), data_out(0)); | ||

| + | end RTL;</source> | ||

| + | |||

| + | ----- | ||

| + | '''оператор when else''' | ||

| + | <source lang="vhdl">entity example_condition is | ||

| + | port ( | ||

| + | x1, x2, x3, x4 : in bit; | ||

| + | condition : in bit_vector(1 downto 0); | ||

| + | F : out bit); | ||

| + | end example_condition; | ||

| + | |||

| + | architecture first of example_condition is | ||

| + | begin | ||

| + | F <= x1 when condition = "00" else | ||

| + | x2 when condition = "01" else | ||

| + | x3 when condition = "10" else | ||

| + | x4; | ||

| + | end first; | ||

| + | |||

| + | architecture second of example_condition is | ||

| + | begin | ||

| + | process (x1, x2, x3, x4, condition ) | ||

| + | begin | ||

| + | if (condition = "00") then | ||

| + | F <= x1; | ||

| + | elsif (condition = "01") then | ||

| + | F <= x2; | ||

| + | elsif (condition = "10") then | ||

| + | F <= x3; | ||

| + | else | ||

| + | F <= x4; | ||

| + | end if; | ||

| + | end process; | ||

| + | end second;</source> | ||

| + | ----- | ||

| + | '''оператор with vs case''' | ||

| + | <source lang="vhdl">entity example_selection is | ||

| + | port ( x1, x2, x3, x4 : in bit; | ||

| + | selection : in bit_vector(1 downto 0); | ||

| + | F : out bit); | ||

| + | end example_selection; | ||

| + | |||

| + | architecture first of example_selection is | ||

| + | begin | ||

| + | with selection select | ||

| + | F <= x1 when "00", | ||

| + | x2 when "01", | ||

| + | x3 when "10", | ||

| + | x4 when others; | ||

| + | end first; | ||

| + | |||

| + | architecture second of example_selection is | ||

| + | begin | ||

| + | process (x1, x2, x3, x4, selection) | ||

| + | begin | ||

| + | case selection is | ||

| + | when "00" => F <= x1; | ||

| + | when "01" => F <= x2; | ||

| + | when "10" => F <= x3; | ||

| + | when others => F <= x4; | ||

| + | end case; | ||

| + | end process; | ||

| + | end second; | ||

| + | </source> | ||

| + | ----- | ||

| + | '''Тригер со сбросом''' | ||

| + | <source lang="vhdl">entity DFF is | ||

| + | port ( | ||

| + | RSTn, CLK, D : in bit; | ||

| + | Q : out bit); | ||

| + | end DFF; | ||

| + | architecture RTL of DFF is | ||

| + | begin | ||

| + | process (RSTn, CLK) | ||

| + | begin | ||

| + | if (RSTn = '0') then | ||

| + | Q <= '0'; | ||

| + | elsif (CLK'event and CLK = '1') then | ||

| + | Q <= D; | ||

| + | end if; | ||

| + | end process; | ||

| + | end RTL;</source> | ||

| + | |||

| + | ----- | ||

| + | '''Сдвиговый регистр на тригерах (структурное описание)''' | ||

| + | <source lang="vhdl"> entity SHIFT is | ||

| + | port ( | ||

| + | RSTn, CLK, SI : in bit; | ||

| + | SO : out bit); | ||

| + | end SHIFT; | ||

| + | architecture RTL1 of SHIFT is | ||

| + | component DFF | ||

| + | port ( | ||

| + | RSTn, CLK, D : in bit; | ||

| + | Q : out bit); | ||

| + | end component; | ||

| + | signal T : bit_vector(6 downto 0); | ||

| + | begin | ||

| + | bit7 : DFF | ||

| + | port map (RSTn => RSTn, CLK => CLK, D => SI, Q => T(6)); | ||

| + | bit6 : DFF | ||

| + | port map (RSTn, CLK, T(6), T(5)); | ||

| + | bit5 : DFF | ||

| + | port map (RSTn, CLK, T(5), T(4)); | ||

| + | bit4 : DFF | ||

| + | port map (CLK => CLK, RSTn => RSTn, D => T(4), Q => T(3)); | ||

| + | bit3 : DFF | ||

| + | port map (RSTn, CLK, T(3), T(2)); | ||

| + | bit2 : DFF | ||

| + | port map (RSTn, CLK, T(2), T(1)); | ||

| + | bit1 : DFF | ||

| + | port map (RSTn, CLK, T(1), T(0)); | ||

| + | bit0 : DFF | ||

| + | port map (RSTn, CLK, T(0), SO); | ||

| + | end RTL1;</source> | ||

| + | |||

| + | ----- | ||

| + | '''Сумматор на N-разрядов''' | ||

| + | <source lang="vhdl">entity adder_N_comp is | ||

| + | port (a, b : in bit_vector (0 to 6); | ||

| + | s : out bit_vector (0 to 6); | ||

| + | c : out bit); | ||

| + | end adder_N_comp; | ||

| + | architecture structural of adder_N_comp is | ||

| + | component add1 | ||

| + | port (b1,b2: in BIT; | ||

| + | c1,s1: out BIT); | ||

| + | end component; | ||

| + | component add2 | ||

| + | port(c1, a1,a2:in BIT; | ||

| + | c2,s2:out BIT); | ||

| + | end component; | ||

| + | signal c_in : bit_vector (0 to 5); | ||

| + | begin | ||

| + | p0: add1 port map (b1 => a(0), b2 => b(0), c1 => c_in(0), s1 => s(0)); | ||

| + | p1: add2 port map (c1=>c_in(0), a1=>a(1), a2=>b(1), c2=>c_in(1), s2=>s(1)); | ||

| + | p2: add2 port map (c1=>c_in(1), a1=>a(2), a2=>b(2), c2=>c_in(2), s2=>s(2)); | ||

| + | p3: add2 port map (c1=>c_in(2), a1=>a(3), a2=>b(3), c2=>c_in(3), s2=>s(3)); | ||

| + | p4: add2 port map (c1=>c_in(3), a1=>a(4), a2=>b(4), c2=>c_in(4), s2=>s(4)); | ||

| + | p5: add2 port map (c1=>c_in(4), a1=>a(5), a2=>b(5), c2=>c_in(5), s2=>s(5)); | ||

| + | p6: add2 port map (c1=>c_in(5), a1=>a(6), a2=>b(6), c2=>c, s2=>s(6)); | ||

| + | end structural;</source> | ||

| + | |||

| + | ----- | ||

| + | '''Оператор generate''' | ||

| + | <source lang="vhdl"> entity SHIFT is | ||

| + | port ( | ||

| + | RSTn, CLK, SI : in bit; | ||

| + | SO : out bit); | ||

| + | end SHIFT; | ||

| + | architecture RTL2 of SHIFT is | ||

| + | component DFF | ||

| + | port ( | ||

| + | RSTn, CLK, D : in bit; | ||

| + | Q : out bit); | ||

| + | end component; | ||

| + | signal T : bit_vector(6 downto 0); | ||

| + | begin | ||

| + | g0 : for i in 7 downto 0 generate | ||

| + | g1 : if (i = 7) generate | ||

| + | bit7 : DFF | ||

| + | port map (RSTn => RSTn, CLK => CLK, D => SI, Q=> T(6)); | ||

| + | end generate; | ||

| + | g2 : if (i > 0) and (i < 7) generate | ||

| + | bitm : DFF | ||

| + | port map (RSTn, CLK, T(i), T(i-1)); | ||

| + | end generate; | ||

| + | g3 : if (i = 0) generate | ||

| + | bit0 : DFF | ||

| + | port map (RSTn, CLK, T(0), SO); | ||

| + | end generate; | ||

| + | end generate; | ||

| + | end RTL2;</source> | ||

| + | |||

| + | </slides> | ||

==Слайд:Работа с редактором EMACS== | ==Слайд:Работа с редактором EMACS== | ||

'''''{{Сн|Emacs }}(Ема́кс, Е́макс, также И́макс) — семейство многофункциональных расширяемых текстовых редакторов.''''' | '''''{{Сн|Emacs }}(Ема́кс, Е́макс, также И́макс) — семейство многофункциональных расширяемых текстовых редакторов.''''' | ||

| − | + | {{Гол|'''''Слово «Emacs» берет начало в аббревиатуре «Editor MACroS», наборе макросов для редактора TECO, написанном Столлманом и другими в 1976 году'''''}} | |

| − | + | ||

| − | + | ||

| + | <s>[http://simhard.com/ftp/files/emacs-22.3-bin-i386.zip Скачать emacs emacs-22.3-bin-i386.zip]</s> или [https://ftp.gnu.org/gnu/emacs/windows/emacs-24.3-bin-i386.zip emacs-24.3-bin-i386.zip] | ||

| + | Для запуска распакуйте zip архив и запустите | ||

| + | |||

| + | .\emacs-23.1-bin-i386\emacs-23.1\bin\runemacs.exe | ||

| + | |||

| + | <!-- [http://vidokq.byethost7.com/mediawiki4intranet/video/emacs_totorial.wmv Небольшая демонстрация возможностей emacs(видео)]--> | ||

===Слайд: Первый запуск === | ===Слайд: Первый запуск === | ||

Команда для запуска | Команда для запуска | ||

| Строка 210: | Строка 713: | ||

* Возможность работы с <big>{{Сн|'''с несколькими окнами одновременно'''}}</big> | * Возможность работы с <big>{{Сн|'''с несколькими окнами одновременно'''}}</big> | ||

* И многое, многое другое полезное. | * И многое, многое другое полезное. | ||

| − | |||

==Слайд: Работа с системой моделирования QuestaSim от Mentor Graphics :step == | ==Слайд: Работа с системой моделирования QuestaSim от Mentor Graphics :step == | ||

| Строка 226: | Строка 728: | ||

** Поддержка пакетов и стандарта '''верификации''' OVM | ** Поддержка пакетов и стандарта '''верификации''' OVM | ||

* Пакет моделирования подключается и в {{Сн|'''MentorGraphics'''}} и в {{Сн|'''Cadence'''}} | * Пакет моделирования подключается и в {{Сн|'''MentorGraphics'''}} и в {{Сн|'''Cadence'''}} | ||

| − | |||

| Строка 233: | Строка 734: | ||

<slides split="-----" width="500"> | <slides split="-----" width="500"> | ||

| − | [[Файл:Questa_adms_ex.jpg | + | [[Файл:Questa_adms_ex.jpg|Окно программы QuestaSim]] |

</slides> | </slides> | ||

| Строка 249: | Строка 750: | ||

* Запуск исполнения и просмотр результата | * Запуск исполнения и просмотр результата | ||

** {{Сн|'''<big>run</big>'''}} | ** {{Сн|'''<big>run</big>'''}} | ||

| + | |||

| + | ===Слайд: Скрин каст=== | ||

| + | <!-- *[[File:Скрин_каст_по_работе_с_QuestaSim.flv]]--> | ||

| + | *[[File:Руководство_по_работе_с_QuestaSim.pdf]] | ||

| + | *[[File:Основные команды QuestaSim.pdf]] | ||

| + | |||

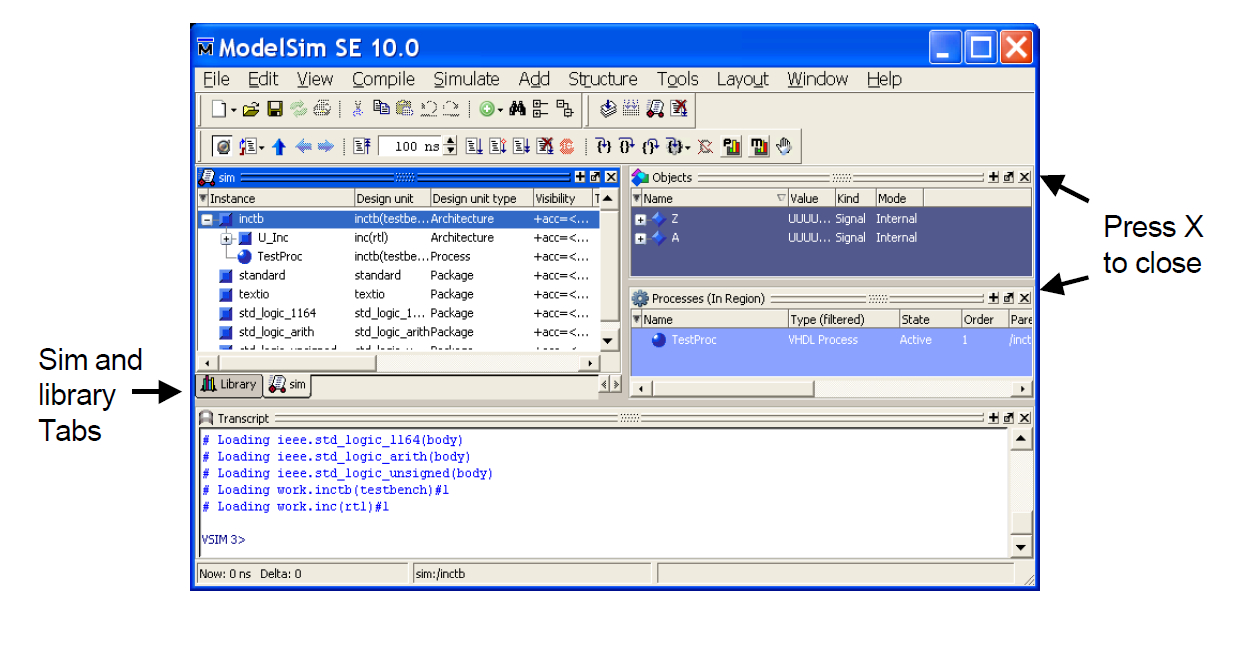

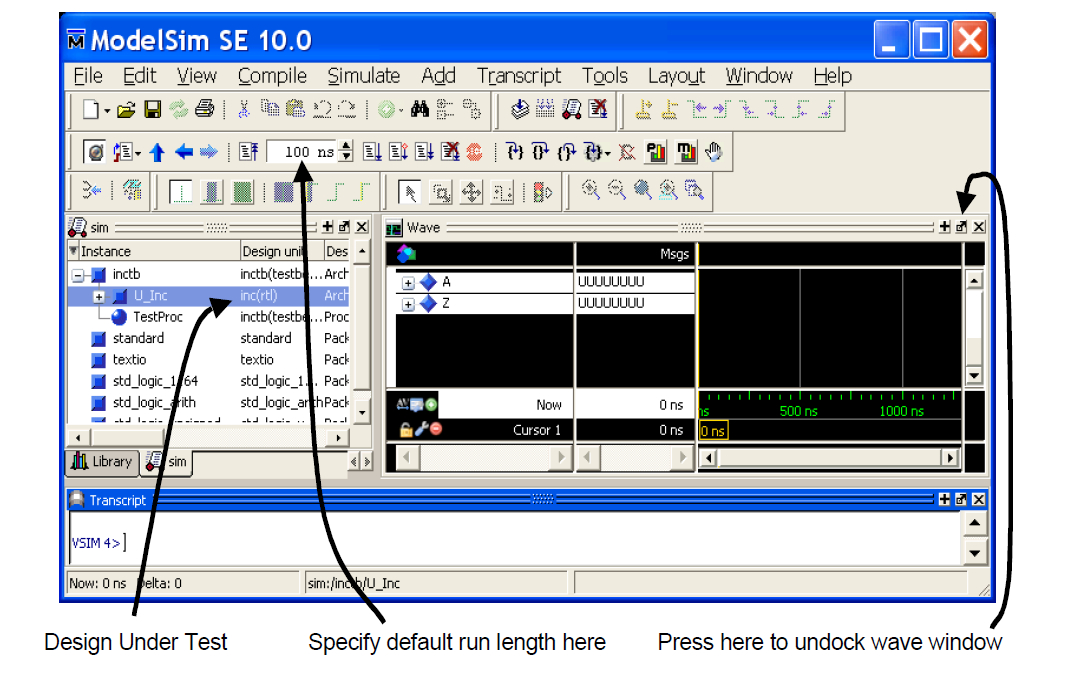

| + | ===Слайд: Основные приемы работы === | ||

| + | <slides split="-----" width="400" > | ||

| + | |||

| + | ''{{Ор|<big>'''Главное окно'''</big>}}'' | ||

| + | |||

| + | [[Файл:Окно_моделсим_10_се.jpg]] | ||

| + | ----- | ||

| + | ''{{Ор|<big>'''Выбор рабочей дирретории '''</big>}}'' | ||

| + | |||

| + | '''"File > Change Directory"''' | ||

| + | |||

| + | [[Файл:Окно_рабочая_дирректория_для_моделсима.jpg]] | ||

| + | ----- | ||

| + | ''{{Ор|<big>'''Создание библиотеки или выбор рабочей'''</big>}}'' | ||

| + | |||

| + | '''"File > New > Library"''' | ||

| + | |||

| + | [[Файл:Окно_создания_бибилиотеки.jpg]] | ||

| + | ----- | ||

| + | ''{{Ор|<big>'''Компиляция проекта'''</big>}}'' | ||

| + | |||

| + | '''"Compile > Compile"''' | ||

| + | |||

| + | [[Файл:Окно_компиляции_проекта.jpg]] | ||

| + | ----- | ||

| + | ''{{Ор|<big>'''Загрузка тестового окружения и запуск моделирования'''</big>}}'' | ||

| + | |||

| + | '''"Simulate > Start Simulation"''' | ||

| + | |||

| + | [[Файл:Запуск_тест_бенча.jpg]] | ||

| + | ----- | ||

| + | ''{{Ор|<big>'''Добавление сигналов для отрисовки и наблюдения'''</big>}}'' | ||

| + | |||

| + | '''"Add > To Wave > ..."''' | ||

| + | |||

| + | [[Файл:Окно_добавления_сигналов_для_отрисовки.jpg]] | ||

| + | ----- | ||

| + | ''{{Ор|<big>'''Запуск моделирования'''</big>}}'' | ||

| + | |||

| + | '''"Simulate > Run > Run..."''' | ||

| + | |||

| + | [[Файл:Окно_моделирования_работа_с_сигнали_выделение.jpg]] | ||

| + | |||

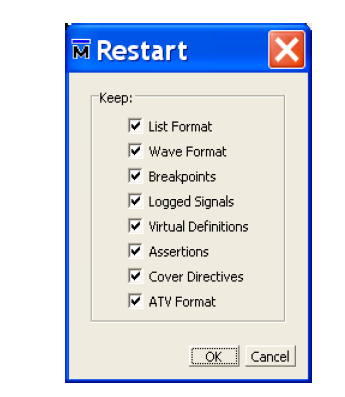

| + | ----- | ||

| + | ''{{Ор|<big>'''Перезапуск моделирования'''</big>}}'' | ||

| + | |||

| + | '''"Simulate > Run > Restart "''' | ||

| + | |||

| + | [[Файл:Окно_перезапуска_моделирвоания.jpg]] | ||

| + | |||

| + | ----- | ||

| + | ''{{Ор|<big>'''Работа с окном отображения сигналов'''</big>}}'' | ||

| + | |||

| + | [[Файл:Работа_с_окном_моделирвоания.jpg]] | ||

| + | ----- | ||

| + | ''{{Ор|<big>'''Разные фичи в окне моделирования'''</big>}}'' | ||

| + | |||

| + | [[Файл:Разные_фичи_в_окне_моделирования.jpg]] | ||

| + | |||

| + | </slides> | ||

| + | [[Категория:Лекции]] | ||

Текущая версия на 00:27, 29 сентября 2015

|

- Тест 1 по RFID системам

- Тест 2 по основам языка VHDL (начальный уровень)

- Тест 3 по языку VHDL (экспертный уровень)

- Тест 4 Среда моделирования

- Тест 5 Верификация VHDL-описания

- Тест 6 Основы языка SystemC

- Заголовок

- Вспомнить все...

- Автор

- Зайцев В.С.

- Нижний колонтитул

- Спец курс (Избранные главы VHDL)/Вспомним VHDL

- Дополнительный нижний колонтитул

- Зайцев В.С., 00:27, 29 сентября 2015

Содержание |

Total Recall

Слайд:Языки описания аппаратуры

- С начала 70-х годов стала актуальна проблема создания стандартного средства документации схем и алгоритмов дискретных систем переработки информации, пригодных как для восприятия человеком, так и для обработки в ЭВМ.

- Этим средством явились языки VHDL и Verilog

- Стандартность (лучше плохой, чем никакого)

- Многоаспектность и многоуровневость

- Схемы

- Тестовые окружения

- Диапазон детализации

- Человеко-машинность

- Язык описания

- Средство документирования

- Было много предшественников

- «МОДИС », «Автокод», «Модис-В78», «MPL», «OCC-2», «Форос», «Алгоритмы», «Пульс», «Симпатия»

- CDL, DDL, ISPS, CONLAN, HILO

VHDL ссылки и литература

Все примеры взяты с сайта БГУИР

Сайт БГУИР с материалами по VHDL

Слайд: Entity

library ieee; use ieee.std_logic_1164.all; entity xc is port ( clk : in std_logic; d : out std_logic); end xc;

Слайд: Architecture

architecture beh of trig is begin -- beh end beh;

Слайд: Process

Слайд: When Else

t1 <= not t1 when clk'event and clk = '1' else t1;

Данная запись является компактным описанием счетного триггера, но она не соответствует стандарту синтезируемого подмножества. Поэтому не все системы синтеза её поддерживают. Например, Leonardo Spectrum синтезирует данную конструкцию, а в ранних версиях Synopsys`а эта запись не поддерживалась.

Примеры кода на VHDL

Логическое ИЛИ

Слайд:Работа с редактором EMACS

Emacs (Ема́кс, Е́макс, также И́макс) — семейство многофункциональных расширяемых текстовых редакторов.

Слово «Emacs» берет начало в аббревиатуре «Editor MACroS», наборе макросов для редактора TECO, написанном Столлманом и другими в 1976 году

Скачать emacs emacs-22.3-bin-i386.zip или emacs-24.3-bin-i386.zip

Для запуска распакуйте zip архив и запустите

.\emacs-23.1-bin-i386\emacs-23.1\bin\runemacs.exe

Слайд: Первый запуск

Команда для запуска

emacs

Слайд: Горячие клавиши

Слайд: Возможности :step

- Знает и подскажет базовые конструкции

- Подсветка синтаксиса

- Анализ существующего кода и добавление уже написанных "слов"

- Автоматическая генерация кода простейшего тестового окружения

- Добавление декларации component

- Добавление декларации instance

- Добавление декларации signal

- Возможность работы с консолью

- Возможность работы с с несколькими окнами одновременно

- И многое, многое другое полезное.

Слайд: Работа с системой моделирования QuestaSim от Mentor Graphics :step

- Где моделировать?

- QuestaSIM

- Язык VHDL, Verilog, SystemC, SystemVerilog

- Смешанное моделирование (все что выше + Spice)

- Автоматизация (поддерживаются скрипты TCL)

- Работа по сети (JobSpy сервер)

- Мощнейший инструмент верификации

- Покрытие кода

- Покрытие переходов

- Проверка значений

- Поддержка пакетов и стандарта верификации OVM

- Пакет моделирования подключается и в MentorGraphics и в Cadence

Слайд: Запуск QuestaSim

Так выглядит окно прогрмаммы QuestaSim

Слайд: Команды QuestaSim :step

- Запуск

- vsim

- Создание библиотеки

- vlib

- Компиляция кода

- vcom

- Запуск моделирования

- vsim name_run_project

- Добавление сигналов

- add wave

- Запуск исполнения и просмотр результата

- run