Спец курс (Избранные главы VHDL)/SystemC — различия между версиями

Vidokq (обсуждение | вклад) (→Слайд: Арифметические, логические, операции присваивания) |

Vidokq (обсуждение | вклад) |

||

| (не показана 21 промежуточная версия 2 участников) | |||

| Строка 1: | Строка 1: | ||

| + | {{ИГСАПР_TOC}} | ||

<slideshow style="custis" headingmark="Слайд:" incmark=":step" scaled="true" > | <slideshow style="custis" headingmark="Слайд:" incmark=":step" scaled="true" > | ||

;title: '''Введение в SystemC.''' | ;title: '''Введение в SystemC.''' | ||

;author: Зайцев В.С. | ;author: Зайцев В.С. | ||

</slideshow> | </slideshow> | ||

| + | {| align=center width=800px | ||

| + | ![[Файл:SystemC_From_the_ground_up.mm]] | ||

| + | |} | ||

| − | |||

| Строка 412: | Строка 415: | ||

[[Файл:Порты_соединение_модулей_экспорт.png]] | [[Файл:Порты_соединение_модулей_экспорт.png]] | ||

[[Файл:Порты_соединение_модулей_экспорт2.png]] | [[Файл:Порты_соединение_модулей_экспорт2.png]] | ||

| − | |||

| − | |||

== Слайд: VHDL и SystemC конструкции == | == Слайд: VHDL и SystemC конструкции == | ||

===Слайд: Entity === | ===Слайд: Entity === | ||

| − | <slides split="-----" width=" | + | <slides split="-----" width="800" > |

| − | {| cellspacing="0" cellpadding=" | + | {| class="standard" cellspacing="0" cellpadding="5" border="1" width="100%" align=center |

| − | | | + | ! {{Фио|'''<big></big>Пример поведенческой модели накопителя (VHDL)'''}} |

| − | {{Фио|'''<big></big>Пример поведенческой модели накопителя ( | + | ! {{Фио|'''<big></big>Пример поведенческой модели <br /> накопителя (SystemVerilog)'''}} |

| − | <source lang="vhdl"> | + | |- |

| + | | align=left valign=top|<source lang="vhdl"> | ||

entity soft is | entity soft is | ||

| − | generic (UART_Speed : integer := 115200; -- UART Speed | + | generic ( |

| − | + | UART_Speed : integer := 115200; -- UART Speed | |

| − | + | System_CLK : integer := 50000000; -- System CLK in Hz | |

| − | + | comand_file : string :="/home/user/comfile.txt" ); | |

port ( | port ( | ||

| − | CLK : out std_logic; | + | CLK : out std_logic; -- system clk |

| − | RST_N : out std_logic; | + | RST_N : out std_logic; -- system reset# |

| − | DATA_IN : out std_logic_vector(7 downto 0); | + | DATA_IN : out std_logic_vector(7 downto 0); -- Transmit data |

| − | DATA_OUT : in std_logic_vector(7 downto 0); | + | DATA_OUT : in std_logic_vector(7 downto 0); -- Recieved data |

| − | RX_VALID : in std_logic; | + | RX_VALID : in std_logic; -- RX buffer data ready |

| − | TX_VALID : out std_logic; | + | TX_VALID : out std_logic; -- Data for TX avaible |

| − | TX_BUSY : in std_logic; | + | TX_BUSY : in std_logic; -- |

RX_BUSY : in std_logic); | RX_BUSY : in std_logic); | ||

| − | |||

end soft; | end soft; | ||

</source> | </source> | ||

| − | + | |align=left|<source lang="cpp"> | |

| − | | | + | |

| − | + | ||

| − | + | ||

| − | <source lang="cpp"> | + | |

| − | + | ||

SC_MODULE (soft_sc_module) | SC_MODULE (soft_sc_module) | ||

{ | { | ||

| Строка 457: | Строка 453: | ||

sc_out < sc_logic > rst_n; | sc_out < sc_logic > rst_n; | ||

sc_out < sc_lv < 8 > > data_in; | sc_out < sc_lv < 8 > > data_in; | ||

| − | |||

public: | public: | ||

| Строка 481: | Строка 476: | ||

} | } | ||

}; | }; | ||

| − | |||

#endif | #endif | ||

</source> | </source> | ||

| Строка 489: | Строка 483: | ||

===Слайд: Architecture === | ===Слайд: Architecture === | ||

| − | <slides split="-----" width=" | + | <slides split="-----" width="800" > |

| − | {| cellspacing="0" cellpadding=" | + | {| cellspacing="0" cellpadding="5" border="1" width="100%" |

| − | + | !{{Фио|'''<big></big>Пример Архитектуры на VHDL'''}} | |

| − | {{Фио|'''<big></big>Пример Архитектуры на VHDL'''}} | + | !{{Фио|'''<big></big>Пример аналогичной конструкции на SystemC'''}} |

| − | <source lang="vhdl"> | + | |- |

| + | | align=left valign=top|<source lang="vhdl"> | ||

architecture beh of soft is | architecture beh of soft is | ||

| Строка 508: | Строка 503: | ||

end beh; | end beh; | ||

</source> | </source> | ||

| − | + | | align=left valign=top|<source lang="cpp"> | |

| − | | | + | |

| − | + | ||

| − | + | ||

| − | <source lang="cpp"> | + | |

SC_MODULE (soft_sc_module) | SC_MODULE (soft_sc_module) | ||

{ | { | ||

| Строка 536: | Строка 527: | ||

tmd.write(btmd); | tmd.write(btmd); | ||

// tmd = btmd; | // tmd = btmd; | ||

| − | //оператор присваивания перегружен и выолнит вызов функции write | + | // оператор присваивания перегружен и |

| + | // выолнит вызов функции write | ||

} | } | ||

~soft_sc_module() | ~soft_sc_module() | ||

| Строка 548: | Строка 540: | ||

===Слайд: Generic === | ===Слайд: Generic === | ||

| − | <slides split="-----" width=" | + | <slides split="-----" width="600" > |

| − | {| cellspacing="0" cellpadding=" | + | {| cellspacing="0" cellpadding="5" border="1" width=100% |

| − | | | + | !{{Фио|'''<big></big>Пример на VHDL'''}} |

| − | {{Фио|'''<big></big>Пример на | + | !{{Фио|'''<big></big>Пример на SystemC (sc_get_param)'''}} |

| − | <source lang="vhdl"> | + | |- |

| + | | align=left valign=top|<source lang="vhdl"> | ||

entity soft is | entity soft is | ||

generic (UART_Speed : integer := 115200; | generic (UART_Speed : integer := 115200; | ||

| − | + | System_CLK : integer := 50000000 | |

); | ); | ||

| − | |||

| − | |||

-- | -- | ||

architecture beh of soft is | architecture beh of soft is | ||

| − | CLK_i <= not CLK_i after 1 ns * ( | + | CLK_i <= |

| + | not CLK_i after 1 ns * (1e9 / System_CLK ); | ||

end beh; | end beh; | ||

</source> | </source> | ||

| − | + | | align=left valign=top|<source lang="cpp"> | |

| − | | | + | |

| − | + | ||

| − | + | ||

| − | <source lang="cpp"> | + | |

SC_MODULE (soft_sc_module) | SC_MODULE (soft_sc_module) | ||

{ | { | ||

| Строка 576: | Строка 564: | ||

tmd("tmd") | tmd("tmd") | ||

{ | { | ||

| − | if (!sc_get_param("System_CLK",System_CLK)) cout << "error get generic"; | + | if (!sc_get_param("System_CLK",System_CLK)) |

| − | if (!sc_get_param("UART_Speed",UART_Speed)) cout << "error get generic"; | + | cout << "error get generic"; |

| + | if (!sc_get_param("UART_Speed",UART_Speed)) | ||

| + | cout << "error get generic"; | ||

period_ns=(1000000000)/System_CLK; | period_ns=(1000000000)/System_CLK; | ||

str = new char [1000]; | str = new char [1000]; | ||

| Строка 914: | Строка 904: | ||

===Слайд: Работа с сигналами === | ===Слайд: Работа с сигналами === | ||

===Слайд: Конструкции С++ === | ===Слайд: Конструкции С++ === | ||

| − | === | + | {{V|24px}}Все конструкции языка С++ разрешено использовать. |

| − | === | + | |

| + | <slides split="-----" width="800" > | ||

| + | {| cellspacing="0" cellpadding="0" border="1" | ||

| + | | | ||

| + | {{Фио|'''<big></big>Пример на VHDL'''}} | ||

| + | <source lang="vhdl"> | ||

| + | procedure skip_space (variable l : inout line) is | ||

| + | variable char : character; | ||

| + | variable flag : boolean:=true; | ||

| + | begin -- skip_space | ||

| + | while flag loop | ||

| + | if l'length = 0 then | ||

| + | flag := false; | ||

| + | elsif l(1) = ' ' then | ||

| + | read(l, char); | ||

| + | else | ||

| + | flag := false; | ||

| + | end if; | ||

| + | end loop; | ||

| + | end skip_space; | ||

| + | </source> | ||

| + | |||

| + | | | ||

| + | {{Фио|'''<big></big>Пример на SystemC'''}} | ||

| + | |||

| + | <source lang="cpp"> | ||

| + | void soft_sc_module :: skip_space (char ** str) | ||

| + | { | ||

| + | bool flag = true; | ||

| + | |||

| + | while ( flag ) { // | ||

| + | if ( !strlen((*str)) ) | ||

| + | //if ( (*str)[0] == '\0' ) //EOS | ||

| + | flag = false; | ||

| + | else | ||

| + | if ((*str)[0]==' ') | ||

| + | (*str) += 1; | ||

| + | else | ||

| + | flag = false; | ||

| + | } | ||

| + | } | ||

| + | </source> | ||

| + | |} | ||

| + | </slides> | ||

| + | |||

===Слайд: Управление процессом моделирования (сообщения, запуск останов моделирования)=== | ===Слайд: Управление процессом моделирования (сообщения, запуск останов моделирования)=== | ||

| − | == | + | {{V|24px}}Для запуска останова и контроля выполнения есть так же встроенные функции. |

| + | |||

| + | <slides split="-----" width="800" > | ||

| + | {| cellspacing="0" cellpadding="0" border="1" | ||

| + | | | ||

| + | {{Фио|'''<big></big>Пример на VHDL'''}} | ||

| + | <source lang="vhdl"> | ||

| + | wait until f_get_answer or f_timer; --ждем пока придет ответ или пройдет время | ||

| + | assert not f_timer report "превышено время ожидания ответа 1 мс" severity FAILURE; | ||

| + | </source> | ||

| + | |||

| + | | | ||

| + | {{Фио|'''<big></big>Пример на SystemC'''}} | ||

| + | |||

| + | <source lang="cpp"> | ||

| + | wait ( f_get_answer.posedge_event() | f_timer.posedge_event() ); | ||

| + | if ( f_timer ) {cout << "превышено время ожидания ответа 1 мс";sc_stop();} | ||

| + | |||

| + | </source> | ||

| + | |} | ||

| + | </slides> | ||

| + | |||

== Слайд: Запуск моделирования только SystemC описания == | == Слайд: Запуск моделирования только SystemC описания == | ||

== Слайд: Запуск моделирования SystemC описания и VHDL(верхний уровень) == | == Слайд: Запуск моделирования SystemC описания и VHDL(верхний уровень) == | ||

| − | Для запуска моделирования | + | '''Для запуска моделирования:''' |

| + | |||

# {{ЖЛампа|24px}}Скачать и установить в корневую дирректорию компилятор {{Зел|'''gcc-4.2.1-mingw32vc9'''}} | # {{ЖЛампа|24px}}Скачать и установить в корневую дирректорию компилятор {{Зел|'''gcc-4.2.1-mingw32vc9'''}} | ||

# {{V|24px}}Если компилятор установлен то переходим на следующий пункт | # {{V|24px}}Если компилятор установлен то переходим на следующий пункт | ||

| − | # Скомпилировать описание: {{Сн|'''<big>sccom -work <library></big>'''}} | + | # '''Скомпилировать''' описание: {{Сн|'''<big>sccom -work <library></big>'''}} |

| − | # Преобразовать выходной файл в исполняемый {{Сн|'''<big>sccom -link -work <library></big>'''}} | + | # '''Преобразовать''' выходной файл в исполняемый {{Сн|'''<big>sccom -link -work <library></big>'''}} |

| − | # Запустить моделирование без опций оптимизации <source lang="text">vsim voptargs=+acc work sc_module </source> | + | # '''Запустить''' моделирование без опций оптимизации <source lang="text">vsim voptargs=+acc work sc_module </source> |

| + | |||

== Слайд: Запуск моделирования SystemC описания и VHDL(верхний уровень) пример == | == Слайд: Запуск моделирования SystemC описания и VHDL(верхний уровень) пример == | ||

| Строка 949: | Строка 1006: | ||

[[Файл:Старт_моделирования.jpg]] | [[Файл:Старт_моделирования.jpg]] | ||

</slides> | </slides> | ||

| + | ==Пример исходника одинаковых описаний на VHDL и SystemC== | ||

| + | |||

| + | * {{ЖЛампа|24px}}[[Файл:Soft.cpp.pdf]] | ||

| + | * {{ЖЛампа|24px}}[[Файл:Soft.h.pdf]] | ||

| + | * {{V|24px}}[[Файл:Soft.vhd.pdf]] | ||

Текущая версия на 13:18, 2 декабря 2013

- Тест 1 по RFID системам

- Тест 2 по основам языка VHDL (начальный уровень)

- Тест 3 по языку VHDL (экспертный уровень)

- Тест 4 Среда моделирования

- Тест 5 Верификация VHDL-описания

- Тест 6 Основы языка SystemC

- Заголовок

- Введение в SystemC.

- Автор

- Зайцев В.С.

- Нижний колонтитул

- Спец курс (Избранные главы VHDL)/SystemC

- Дополнительный нижний колонтитул

- Зайцев В.С., 13:18, 2 декабря 2013

Основы языка SystemC

Слайд:Типы данных (Форматы и способ представления данных)

Слайд:Типы данных (native)

// Пример типа данных C++ int spark_offset; unsigned repairs = 0 ; // Count repair unsigned long mileage; // Miles driven short int speedometer; // -20.. 0.. 100 MPH float temperature; // Engine temp in C double time_of_last_request; //Time of bus std:: string license_plate; // Text for license const bool WARNING_LIGHT = true; // Status enum compass {SW,W,NW,N,NE,E, SE, S} ;

Слайд:Типы данных (Arithmetic)

// Пример целочисленных типов данных C++ sc_int<LENGTH> NAME...; sc_uint<LENGTH> NAME...; sc_bigint<BITWIDTH> NAME...; sc_biguint<BITWIDTH> NAME...; // SystemC integer data types sc_int<5> seat_position=3; //5 bits: 4 plus sign sc_uint<13> days_SLOC(4000); //13 bits: no sign sc_biguint<80> revs_SLOC; // 80 bits: no sign

Слайд:Типы данных (Boolean)

// Пример типа данных SystemC sc_bit NAME...; sc_bv<BITWIDTH> NAME...;

- sc_bit и sc_bv могут принимать значения: SC_LOGIC_1 и SC_LOGIC_0.

- Для сокращения типов, можно использовать Log_1 и Log_0 или ‘1’ и ‘0’.

- Над этим типом данных возможно выполнение битовых операций and, or, xor (&,|, ^).

- Для обращения к отдельным битам и массивам [], range().

sc_bit flag(SC_LOGIC_1); // more efficient to use bool sc_bv<5> positions = "01101"; sc_bv<6> mask = "100111"; sc_bv<5> active = positions & mask;// 00101 sc_bv<1> all = active. and_reduce (); // SC_LOGIC_0 positions. range (3,2) = "00"; // 00001 positions [2] = active[0] ^ flag;

Слайд:Типы данных ( многозначные (ZX10))

// Пример типа данных SystemC sc_logic NAME[,NAME]...; sc_lv<BITNIDTH> NAME[,NAME ]...; sc_logic buf(sc_dt::Log_Z); sc_lv<8> data_drive ("zz01XZ1Z"); data_drive.range (5,4) = "ZZ";// ZZZZXZ1Z buf = '1';

Слайд:Операторы SystemC

Слайд:Главный модуль MAIN

int main(int argc, char* argv[]) { BODY_OF_PROGRAM return EXIT_CODE; // }

int sc_main(int argc, char* argv[]) { //ELABORATION sc_start(); // <-- Simulation begins & ends // in this function! //[POST-PROCESSING] return EXIT_CODE; // }

Слайд: Модуль

#include <systemc.h> SC_MODULE(module_name) { MODULE_BODY };

Содержит:

- Порты

- Каналы связи

- Объявления переменных для хранения данных

- Другие модули с большей вложенностью

- Конструктор

- Деструктор

- Функции -процессы

- Вспомогательные функции

Слайд: Конструктор (SC_CTOR)

SC_CTOR(module_name) : Initialization // могут отсутствовать объявления и инициализация сигналов { Subdesign_Allocation Subdesign_Connectivity Process_Registration Miscellaneous_Setup }

- Объявление под модулей

- Подключение и соединение с подмодулями

- Регистрация процессов на SystemC

- Объявление списка чувствительности

- Разнообразные пользовательские объявления

Слайд: Конструктор (SC_HAS_PROCESS)

//FILE: module_name.h SC_MODULE(module_name) { SC_HAS_PROCESS(module_name); module_name(sc_module_name instname[, other_args…]) : sc_module(instname) [, other_initializers] { CONSTRUCTOR_BODY } };

- Все возможности конструктора SC_CTOR

- Альтернативный метод создания модуля

- Позволяет создавать конструктор с аргументами(+ к имени модуля)

- Используется, если желаете расположить конструктор в файле описания .cpp (не в файле .h)

Слайд: Процесс SC_THREAD

SC_MODULE(simple_process_ex) { SC_CTOR(simple_process_ex) { SC_THREAD(my_thread_process); } void my_thread_process(void); };

SC_THREAD в SystemC:

- аналог initial block в Verilog

- process без списка чувствительности с оператором wait() в VHDL.

Слайд:Введение времени

Единицы измерения времени

SC_SEC // seconds SC_MS // milliseconds SC_US // microseconds SC_NS // nanoseconds SC_PS // picoseconds SC_FS // femtoseconds

sc_time t_PERIOD(5, SC_NS) ; sc_time t_TIMEOUT (100, SC_MS) ; sc_time t_MEASURE, t_CURRENT, t_LAST_CLOCK; t_MEASURE = (t_CURRENT-t_LAST_CLOCK) ; if (t_MEASURE > t_HOLD) { error ("Setup violated") }

Слайд:Запуск выполнения sc_start()

Функция запускающая выполнения главного процесса

Пример запуска моделирования на 60 секунд модельного времени

int sc_main(int argc, char* argv[]) { // args unused simple_process_ex my_instance ("my_instance"); sc_start(60.0,SC_SEC); // Limit sim to one minute return 0 ; }

Слайд:Контроль текущего времени моделирования sc_time_stamp ()

std::cout << " The time is now " << sc_time_stamp() << "!" << std::endl;

После запуска моделирования в консоли получим

The time is now 0 ns!

Слайд: Остановка выполнения моделирования wait(sc_time)

Функция останавливающая выполнение процесса до заданного времени или до прихода события

void simple_process_ex::my_thread_process (void) { wait (10,SC_NS); std::cout<< "Now at "<< sc_time_stamp() << std::endl; sc_time t_DELAY(2,SC_MS); // keyboard debounce time t_DELAY *= 2; std::cout<< "Delaying "<< t_DELAY<< std::endl; wait(t_DELAY); std::cout << "Now at " << sc_time_stamp() << std::endl; }

% . /run_example Now at 10 ns Delaying 4 ms Now at 4000010 ns

Слайд:События sc_event

Слайд:События SC_THREAD::wait()

Процесс SC_THREAD процес выполняющийся один раз!!, для управления работой такого процесса используют функцию задержки выполнения wait

wait(time); wait(event); wait(event1 | event2) // до прихода любого из событий wait(event1 & event2) // до прихода всех событий вместе wait(timeout, event); // до прихода события ожидает в течении времени wait ( timeout, event1 | event2 ) wait ( timeout, event1 & event2 ) wait(); // ожидание дельта цикла выполнения, статическая задержка

Слайд:Запуск события (установка,назначение)

Для запуска события используется атрибут .notify()

Он выполняет запуск событий, отсчет времени идет от запуска моделирования. Для сброса точки отсчета используют .cancel()

sc_event action; sc_time now(sc_time_stamp()); //вытягиваем текущее время моделирования //стартуем событие немедленно action.notify(); //следующее событие через 20 ms от текущего момента action.notify(20, SC_MS); //переопределим событие на время 1.5 ns от текущего момента action.notify(1.5,SC_NS); //продублируем событие (не имеет эффекта) action.notify(1.5, SC_NS); //зададим событие от предыдущего на 1.5 ns action.notify(3.0,SC_NS); //запустим дельта цикл (не имеет эффекта) action.notify(SC_ZERO_TIME); //сбросим время задания события action.cancel(); //зададим событие на 20 fs после сброса action.notify(20,SC_FS);

Слайд:Процесс со списком чувствительности SC_METHOD

SC_METHOD(process_name);

![]() Список чуствительности задаеться после ключевого слова sensitive

Список чуствительности задаеться после ключевого слова sensitive

sensitive << event [<< event] ;// поточный стил sensitive (event [, event] ); // стиль с использованием функции

Слайд:dont_initialize()

![]() Отменяет начальную установку значений

Отменяет начальную установку значений

- После запуска моделирования конструктор создает модуль и инициализирует все процессы и переменные.

- Это заставляет выполниться всем методам работающим по событию по одному разу во время запуска если событие устанавливалось в значение.

- Для исключения начального выполнения используется функция dont_initialize()

Слайд: Стек событий sc_event_queue

![]() Событие можно задать не только от начального момента времени, а и от текущего.

Событие можно задать не только от начального момента времени, а и от текущего.

Для этого используется функция sc_event_queue()

sc_event_queue action; sc_time now(sc_time_stamp()); action.notify(20, SC_MS); action.notify(1.5,SC_NS); action.notify(1.5,SC_NS); action.notify(3.0,SC_NS); action.notify(SC_ZERO_TIME); action.notify(1,SC_SEC); action.cancel_all();

Слайд:Совместное использование ресурсов

- При совместном использовании ресурсов, шин, памяти нужно разграничить область полномочий каждого процесса.

- Иначе при одновременной, к примеру записи будет происходить сбой или некорректная запись.

sc_mutex NAME; // блокируем mutex NAME (ждем пока разблокируется) NAME.lock(); // Возвращает статус состояния блокировки NAME.try lock() // Снимает блокировку NAME.unlock();

Если управлением доступом к нескольким ресурсам

sc_semaphore NAME(COUNT); // блокируем mutex NAME (ждем пока разблокируеться) NAME.wait(); // Возвращает статус состояния блокировки NAME.trywait() //Возвращает число свободных ресурсов NAME.get_value() // Снимает блокировку NAME.post();

Слайд:Иерархия и структура проекта

Слайд:Иерархия и структура проекта (sc_main)

![]() Подключение и создание модуля внутри главного модуля аналогично созданию объекта заданного класса

Стандартная конструкция блока хранения информации для RFID

Подключение и создание модуля внутри главного модуля аналогично созданию объекта заданного класса

Стандартная конструкция блока хранения информации для RFID

//FILE: main.cpp #include "Wheel.h" int sc_main(int argc, char* argv[]) { Wheel wheel_FL("wheel_FL"); Wheel wheel_FR("wheel_FR"); sc_start(); } |

//FILE: main.cpp #include "Wheel.h" int sc_main(int argc, char* argv[]) { Wheel* wheel_FL; // pointer to FL wheel Wheel* wheel_FR; // pointer to FR wheel wheel_FL = new Wheel ("wheel_FL"); // create FL wheel_FR = new Wheel ("wheel_FR"); // create FR sc_start(); delete wheel_FL; delete wheel_FR; } |

Слайд:Иерархия и структура проекта (SC_MODULE)

![]() Подключение и создание модуля внутри другого модуля аналогично созданию объекта заданного класса, внутри другого класса. Поэтому объявления производиться в конструкторе верхнего модуля

Подключение и создание модуля внутри другого модуля аналогично созданию объекта заданного класса, внутри другого класса. Поэтому объявления производиться в конструкторе верхнего модуля

//FILE:Body.h #include "Wheel.h" SC_MODULE(Body) { Wheel wheel_FL; Wheel wheel_FR; SC_CTOR(Body) : wheel_FL("wheel_FL"), //initialization wheel_FR("wheel_FR") //initialization { // other initialization } }; } |

//FILE:Body.h #include "Wheel.h" SC_MODULE(Body) { Wheel* wheel_FL; Wheel* wheel_FR; SC_CTOR(Body) { wheel_FL = new Wheel("wheel_FL"); wheel_FR = new Wheel("wheel_FR"); // other initialization } }; } |

Слайд:Порты - точки подачи и снятия внешних воздействий

Слайд:Типы портов

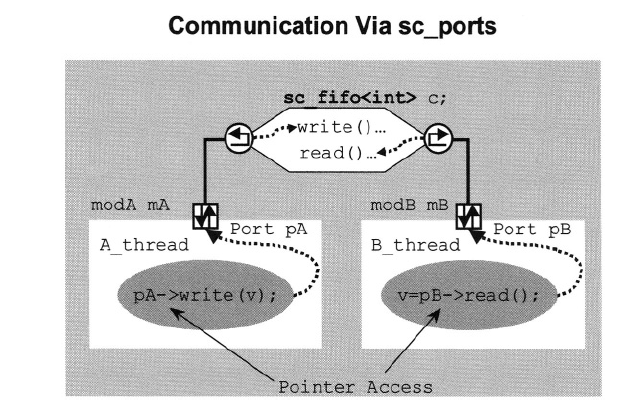

- sc_port - аналог inout порта в языке VHDL

- sc_in - аналог in порта в языке VHDL

- sc_out - аналог out порта в языке VHDL

- sc_export - внешний порт, порт который позволяет получить доступ к private данным модуля, но иерархически модулю не принадлежит.

![]() Механизм использования sc_export порта напоминает доступ к сигналам по иерархии, как в VHDL-2008.

Механизм использования sc_export порта напоминает доступ к сигналам по иерархии, как в VHDL-2008.

Слайд:Порты - точки подачи и снятия внешних воздействий

Слайд: VHDL и SystemC конструкции

Слайд: Entity

Слайд: Architecture

Слайд: Generic

Слайд: Process без списка чувствительности

Слайд: Process со списком чувствительности (пример 1)

Слайд: Process со списком чувствительности (пример 2)

Слайд: Работа с файлами

Слайд: Работа с файлами

Слайд: Работа с функциями

Слайд: Работа с сигналами

Слайд: Конструкции С++

![]() Все конструкции языка С++ разрешено использовать.

Все конструкции языка С++ разрешено использовать.

Слайд: Управление процессом моделирования (сообщения, запуск останов моделирования)

![]() Для запуска останова и контроля выполнения есть так же встроенные функции.

Для запуска останова и контроля выполнения есть так же встроенные функции.

Слайд: Запуск моделирования только SystemC описания

Слайд: Запуск моделирования SystemC описания и VHDL(верхний уровень)

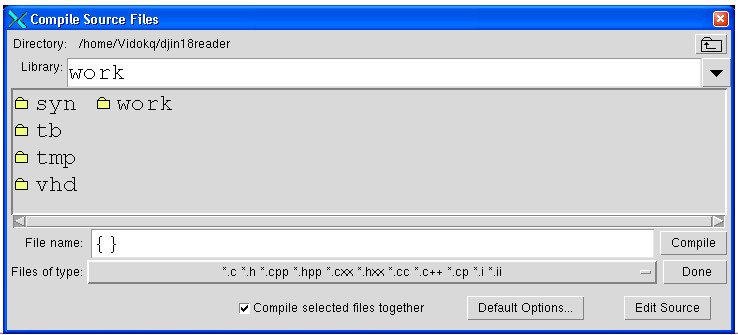

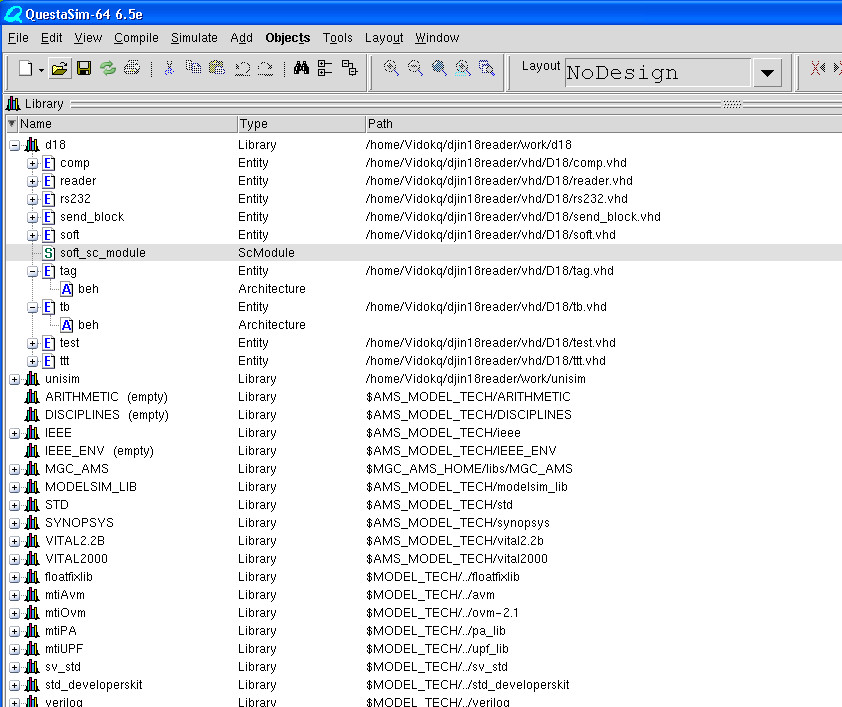

Для запуска моделирования:

-

Скачать и установить в корневую дирректорию компилятор gcc-4.2.1-mingw32vc9

Скачать и установить в корневую дирректорию компилятор gcc-4.2.1-mingw32vc9

-

Если компилятор установлен то переходим на следующий пункт

Если компилятор установлен то переходим на следующий пункт

- Скомпилировать описание: sccom -work <library>

- Преобразовать выходной файл в исполняемый sccom -link -work <library>

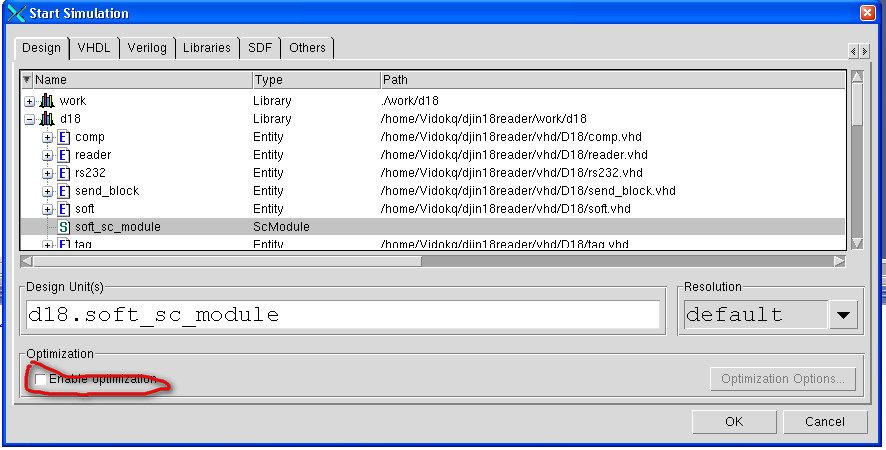

- Запустить моделирование без опций оптимизации

vsim voptargs=+acc work sc_module